基于Camera Link接口的图像跟踪系统的设计

目前使用的图像跟踪系统前端输入信号一般都是PAL制式的标准全电视信号,每20 ms一场,每40 ms一帧。模拟信号经过视频解码器转换成720×576大小的数字信号后,再对其中的目标进行分割、识别和跟踪,并准确计算出目标的位置角度偏差,并传给伺服机构。在某系统中要求能对3×3像素大小的小目标进行精确跟踪,为了达到跟踪精度,可以提高图像输入的帧频和提高图像输入的分辨率,因此前端采用了 DALSA公司的一款基于Camera Link接口的数字摄像机,该相机的帧频为100 Hz,分辨率高达1 400×1 024。这样帧处理时间就只有10 ms,考虑到系统的实时性,我们采用了TI公司的高性能的DSP芯片TMS320C6414和高性能FPGA芯片EP2S30F672为核心的硬件处理平台。

本文引用地址:https://www.eepw.com.cn/article/166928.htm1 系统硬件结构和工作原理

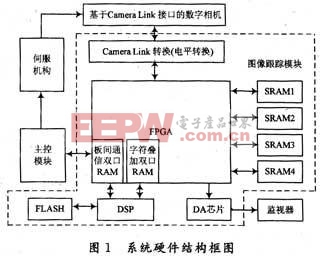

整个图像跟踪模块的结构图如图1中虚线框所示,整个系统包括以FPGA为核心的图像采集和预处理单元,以DSP为核心的图像处理单元以及由FPGA控制的图像显示单元。

由于采集、处理、显示均要访问存储器,为了降低成本,用普通的异步SRAM构成。按照功能来分可分为采集处理用SRAM组和采集显示用SRAM组,每组分别包括两片SRAM,其读写逻辑由FPGA控制,采用乒乓方式进行切换。

对于采集处理部分,第K帧时,SRAM1由FPGA控制写入图像数据,同时SRAM2由DSP读数进行处理;第K+1帧时则相反,SRAM2由FPGA控制写入图像数据,同时SRAM1由DSP读数进行处理。

对于采集显示部分,第K帧时,SRAM3由FPGA控制写入图像数据,同时SRAM4由FPGA读数进行显示;第K+1帧时则相反,SRAM4由FPGA控制写入图像数据,同时SRAM3由FPGA读数进行显示。

整个系统工作过程都是这样的:其中图像采集单元经由差分转换芯片后变成LVTTL信号,直接连至FPGA,由FPGA控制数字图像的采集,进行图像预处理后,将图像数据存储在SRAM中,给DSP发出中断信号,DSP响应中断后,从SRAM中读取一帧图像数据后,进行图像分割、目标提取、目标跟踪算法,计算出方位和高度角偏差分量,将结果通过FPGA的片内的板间通信双口RAM传递给主控模块,主控模块再调整伺服机构保证被跟踪的目标处于视场中心。

主控模块还可以将系统的一些状态变量实时的通过板间通信双口RAM传给DSP,DSP根据这些状态生成需要显示的字符,将这些字符写入到FPGA片内字符叠加双口RAM中。FPGA读取显示RAM中的图像数据和片内字符叠加双口RAM内的数据,在原图上叠加十字丝和波门,以及系统的一些状态字符信息,按照 PAL制式时序向DA芯片送视频数据,这样监视器就可以输出标准的PAL制式的图像。

2 各个单元设计

2.1 基于Camera Link接口的图像采集和预处理单元

Camera Link是一种基于视频应用发展而来的接口,它解决了视频数据输出和采集之间的速度匹配问题。Camera Link数据的传输率非常高,可达1 Gb/s,采用了LVDS格式,抗噪性能好。Camera Link的信号包括三个部分:串行通信部分、相机控制部分、视频信号部分,基于Camera Link接口的图像采集单元详图见图2,每个部分采用专门的差分转换芯片。串行通信部分则将异步串口转换成标准的RS 232电平,这样可以由主控机对相机的曝光时间、对比度等设置进行调节。相机控制部分包括4对差分信号,用来对相机进行控制,比如相机的外同步信号输入控制,可以由FPGA进行控制。视频部分的28 b LVTTL信号是关键控制部分,它们直接接在FPGA上,由FPGA来控制采集的时序。

评论