基于Camera Link接口的图像跟踪系统的设计

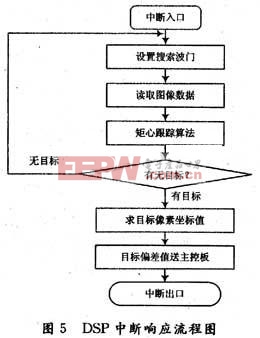

以常用的最简单的矩心跟踪算法为例,DSP每次响应中断后,主要进行的工作是:首先设定搜索的波门,将波门内的数据通过DMA方式快速搬移到片内存储器,然后用矩心跟踪算法进行处理,直至搜索出目标后,将目标的像素的位置偏差计算出来并送给主控板。

系统要求输出标准的PAL制式的模拟视频,由于PAL制式视频场频为50 Hz,帧频为25 Hz,所以对于前端高分辨率高帧频的数字图像,必须降频输出,且分辨率也要降低。选用专用的图像DA芯片ADV7123,该芯片输入位宽为10 b,可以转换的数据速率可达240 MHz。因为标准的PAL制式视频一帧只能显示有效行576行,对于1 024行的数据图像只能隔行显示512行,且奇场256行,偶场256行。所以对于采集的图像来说行方向上是降低了分辨率,但在列的方向上不降低分辨率。

由前面可知,由于采集显示采用乒乓结构,但是由于显示是隔行抽点显示的,且显示的频率帧频为25 Hz,所以在采集部分时,应当隔行取数据存储,且每2帧才更新一次采集的数据。不像采集处理部分一样,每帧都要更新采集的数据。

控制ADV7123的时钟信号、复合同步信号、复合消隐信号均由FPGA产生。与电视相关的行、场同步和消隐信号正是PAL制式模拟视频信号生成的关键。

FPGA 认通过对数字相机下来的80 MHz时钟倍频后,经过时钟计数和逻辑组合运算获得所需要的各种同。步时序信号。ADV7123的时钟信号根据80 MHz时钟先2倍频后蒋5分频而成,即像素时钟频率为32 MHz,周期为31.25 ns。生成的图像大小为1 400×576像素,即每场图像有288行,每行有1 400个像素点。系统采用PAL制式的隔行扫描方式,场周期时间为20 ms,行周期为64μs,所以每场包含312.5个行周期,但场消隐的高电平持续288个行周期,只要调整场消隐信号的起始位置,就很容易使视频图像的输出位于屏幕的正中间。行场同步信号和消隐信号的实现思路基本上一样:对时钟计数,计到某一个数值时,使输出的信号翻转(由低电平到高电平或者由高电平到低电平),计数器的周期和翻转的周期根据不同的参数而有所不同。由于这些时序是在FPGA中编程实现,很容易调整和修改。

至于字符叠加过程,DSP按照在图像上实际叠加字符的位置和大小将要叠加的字符点阵写入到FPGA片内双口RAM中(显示字符的地方写二进制的1,显示图像的地方写二进制的0),显示输出的每一帧,FPGA读取字符叠加双口RAM,根据其值来决定是输出采集的图像还是输出叠加字符。这样通过DSP和FPGA 的配合,可以灵活地叠加任何字符,DSP可以根据系统的任何状态变化来改变字符叠加RAM中的值,因此保证系统具有良好的人机交互界面。

3 结语

以高性能DSP和FPGA为核心,对Camera Link接口的数字相机进行图像采集,采用数字图像处理技术,建立了一个实时的图像跟踪系统。该系统体积小、重量轻、可靠性高,具有良好的人机交互界面,已经成功地应用在实际项目中。

评论