一种超低功耗5.8GHz双模前置分频器设计

摘要:基于目前流行的TSPC高速电路,利用TSMC90nm 1.P9M 1.2V CMOS工艺设计了高速、低压、低功耗32/33双模前置分频器,其适用于WLAN IEEE802.1la通信标准。运用Mentor Graphics Eldo对该电路进行仿真,仿真结果显示,工作在5.8GHz时功耗仅0.8mW,电路最高的工作频率可达到6.25GHz。

关键词:双模前置分频器 单相时钟 高速度 低功耗

0 引言

随着移动通信技术的迅速发展,对射频电路的高速、低功耗要求日益增长。基于锁相环(PLL)结构的频率合成器是收发机前端电路的重要组成部分,对为混频器提供纯净的本振信号,具有重要地位。在PLL中,压控振荡器(VCO)和前置分频器(Prescaler)是工作在最高频率的两个模块,它们是限制PLL工作频率的主要瓶颈,因此提高前置分频器的工作速度是解决限制PLL工作频率上限的一个关键因素。为了满足高频通信的要求,必须对前置分频器和VCO进行高速、低功耗的优化设计。

双模前置分频器以D触发器为主要单元。近年来涌现了很多不同结构的高速D触发器。第1种是静态SCL结构,由ECL电路结构演变而成。与传统的静态分频器相比,由于它的摆幅较小,所以工作速度快。但是典型SCL结构的2分频电路包括尾电流源在内至少需要18个MOS管,MOS管无法做到小尺寸,导致输入电容很大甚至超过了管子本身的电容,所以SCL分频器功耗较高。第2种是动态的TSPC(单相时钟)结构,它采用单相时钟的TSPC技术使构成分频器的元件数目减少,可以提高电路的工作速度,同时这种电路的功耗极低,所以经常在前置分频器中采用。TSPC分频器的不足是噪声性能不佳,因为动态单端结构比SCL结构更容易受噪声的影响。第3种是注锁式(iniected-locked)电路,由于要使用电感器,因而它的体积过大且工艺难度高,很少被应用。具体采用哪种电路结构应视情况而定。

本文采用动态TSPC结构,利用TSMC 90nm 1P9M 1.2VCMOS工艺,设计了一个适用于WLAN IEEE802.11a标准的双模前置分频器,具有高速、低压、低功耗的特点。

1 电路设计

1.1 电路总体架构

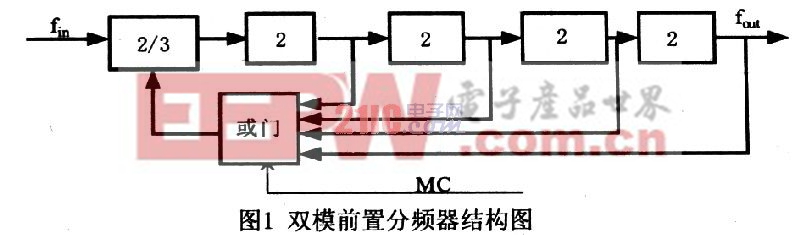

双模前置分频器的基本结构如图1所示,包括三个部分:同步2/3分频器,由异步除2分频器构成的分频器链,以及反馈部分。控制信号MC控制分频比,当MC=1时为32分频,当MC=O时为33分频。

图l双模前置分频器结构图

本设计基于上述传统结构,通过减少高频同步分频器单元中MOS管的个数,达到降低功耗的目的。

评论