一种超低功耗5.8GHz双模前置分频器设计

1.2 同步分频器设计

同步2/3分频器的结构框图如图2所示,它是整个分频器工作频率最高的部分,亦是决定前置分频器速度和功耗的关键部分。本文引用地址:http://www.eepw.com.cn/article/157518.htm

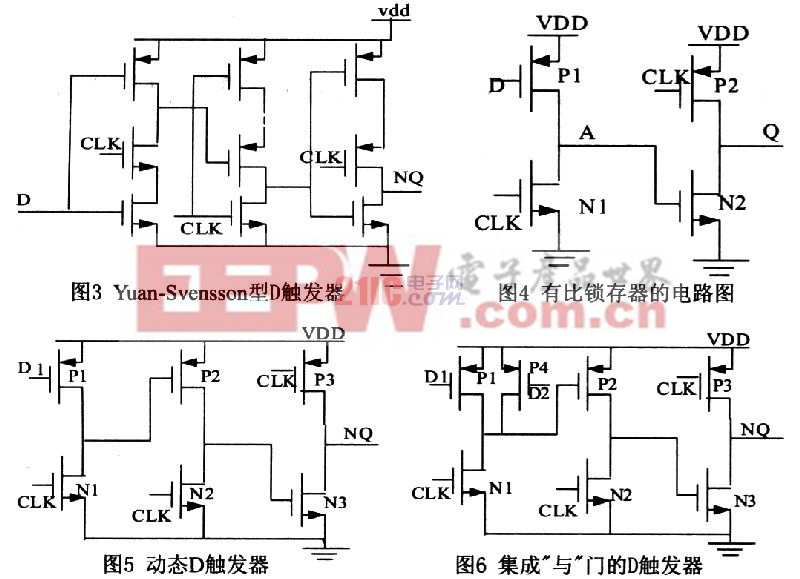

MC为逻辑高电平时,电路实现2分频;MC为逻辑低电平时,电路实现3分频。采用同步2/3分频器,大大减少了工作在高频部分MOS管的数目,从而同步部分的功耗有所下降。同时将“与”门设计在D触发器中。这种集成“与”门的触发器不但简化了电路设计,而且避免了单独设计逻辑门所带来的寄生参数的影响,减少了速度损失,从而很好地缓解了工作速度和功耗之间的矛盾。

1.3 优化功耗

从以上的分析可以看出,电路最大的功耗来自同步2/3分频器,但无论是同步2/3分频器还是异步分频器链都必须采用D触发器,因此设计好高速低功耗的D触发器是影响整个分频器速度和功耗的关键。

图3为常用的Yuan-Svensson型D触发器(下降沿触发),这种电路采用动态CMOS技术,从左至右由一个N-C2MOS级,一个P-PrechargeCMOS级和一个P-C2MOS级组成。相对于传统的静态分频器,它的各项性能已经有了明显的改善,但是由于大多数MOS管既是前级的负载管又是后级的驱动管,每一级三个MOS管叠加带来了大的RC延迟,所以就算减小其尺寸也不能提高速度。为此我们对图3中的C2MOS电路进行改进,用钟控伪PMOS反相器代替N-C2MOS,这样MOS管的数目、负载电容都有减小。同样用钟控伪NMOS反相器代替PC2MOS,构成图4所示的动态有比锁存器,当时钟信号为低(高)电平时锁存器工作在求值(保持)模式,与Yuan-Svensson结构的D触发器相比具有更低的RC,因此减小了功耗和传输延迟。

评论