关于UART通信端口上射频干扰的研究

出现的问题是连接到AD6903GPIO_1引脚的UARTRX信号中出现噪声,每当射频(RF)干扰源出现时,信号平均电压就会远离其期望值。平均电压的偏移幅度取决于RF源的功率和频率。

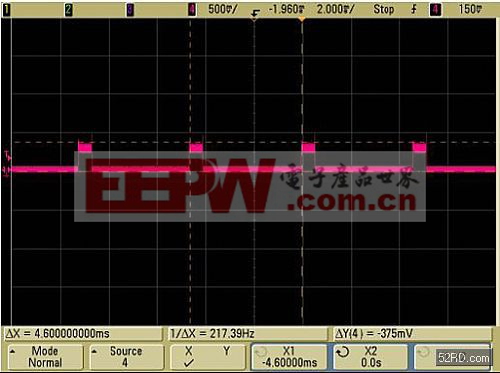

本文引用地址:https://www.eepw.com.cn/article/157492.htm图1显示当射频功率放大器接通时,进入AD6903的GPIO_1引脚上的UARTRX信号受到影响的情况。在图1中,进入AD6903的UARTRX用粉红色表示,来自主处理机的UARTTX信号用紫色表示,功率放大器使能用黄色表示,而AD6903VEXT电源用绿色表示。

当功率放大器接通(黄色)时,从主处理器的TX引脚到AD6903的RX引脚(桃红色)的UART数据传输发生了故障,因为RX信号上升到高低电平之间的中间位置,而与TX信号(紫色)不一致。在第二个脉冲期间,当功率放大器接通时,主处理器的TX引脚和AD6903的RX引脚应该都保持高电平;但是TX引脚上有噪声,而且RX信号下降至其高低电平的中间位置。并且注意VEXT电源电压(绿色)上的噪声增大,并且当功率放大器接通时其值还会略为上升。

然而,问题必须是与功率放大器的使能信号和同一个调制解调器的功率放大器无关,因为从附近其他的电话或信号发生器带来的RF能量也会影响进入AD6903的UARTRX信号。使用信号产生器扫描来检查对射频干扰的易受度时发现,最坏的地方约在840MHz,而在高频或更低的频率上则较好。

在主处理器和AD6903之间的这个信号的串联电阻器被用于使逻辑高电平从3.3V降低到2.8V。这个电阻器的额定阻值是10kΩ。可以用较小的电阻、包括0Ω电阻器来替换之,因为降低阻值可以减小噪声,但是这并不能解决问题,除非用短路线来代替。

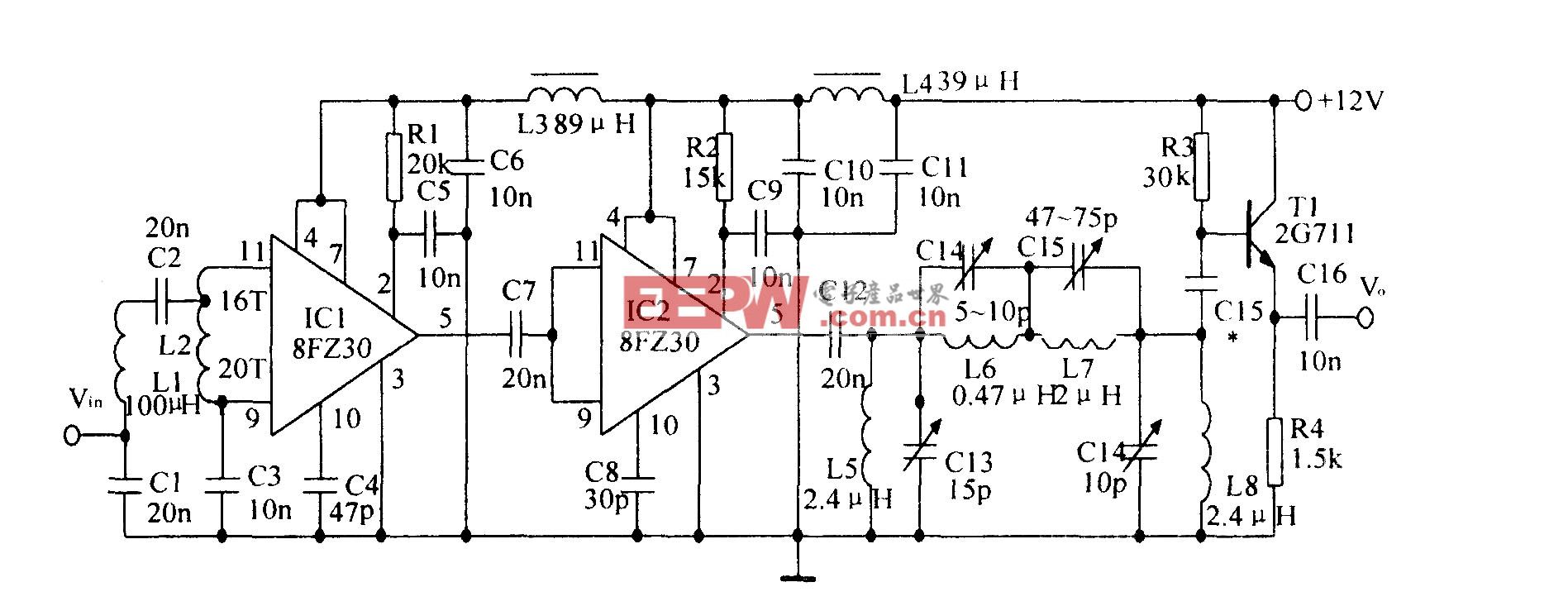

这个问题也不是AD6903才特有的。来自其他厂商的芯片也具有相似的现象。比如,SN74AVCA16425GR的引脚37上也有同样的问题。其功能框图请参考图2。

图2:SN74AVCA16425GR功能框图

这里的1DIR、2DIR为高电平,OE为低电平,因此操作是从A口到B口,引脚37(1A7)将接收来自另一个芯片组的数据。这意味着它是输入型。

在附近存在RF干扰的情况下,即在测试点附近(5米以内)用手机打电话,来测试SN74AVCA16425GR的引脚37上的信号。图3显示当设备不加电时(I/O状态未知),其输出反常;而图4则显示当设备加电(输入状态)时其输出的反常情况。

图3:低电平升高

干扰原理

进入AD6903的UARTRX信号的这种“RF干扰拾取”行为的发生以一个特定的RF频率为中心,而这些信号迹线没有完全被屏蔽。这种现象是可以解释的:主板的印刷导线拾取干扰,因为导线上有寄生电感、寄生电阻和寄生电容,而导线的两端连接的是高阻抗;一侧是一个10kΩ电阻器,另一侧则是CMOS输入。电路板上的导线就像一个具有1/4波长响应的天线。

图4:高电平降低

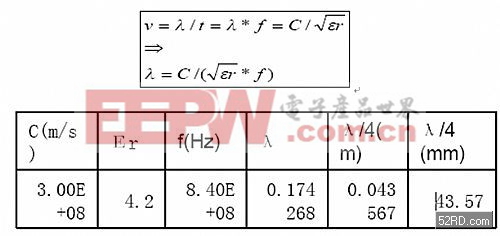

在客户模块中,计算GPIO1导线时,模块上按30mm计算,而主板上则大约为15mm。所以这条线能够拾取RF噪声并对840MHz敏感就不奇怪了。具体可以参考图5。

图5:RF干扰计算公式

评论