适于底层协议栈开发的数据采集与仿真系统

1 数据采集系统

数据采集系统主要完成从正在工作中的通信终端中采集数据的任务。

1.1 采集点的选择

整个通信系统中有多个数据采集切入点可选,可以对中频信号直接采样,也可以对基带信号采样,还可以通过模拟系统中的AD数据接收时序,直接接收AD输出数据。但前两种采集点不能确保采集到的信号数据与DSP输入数据完全一致,而模拟AD数据时序的方式则可能影响DSP与AD之间的主从关系,影响DSP协议栈的正常运行,而且各种外部中断的采集也比较困难。因而最为稳妥的方式是DSP通过数据总线输出其接收到的数据。这种方法的缺点是需要占用DSP少量资源,但这与协议栈运行相比,完全可以忽略不计,不计不会影响协议栈本身的运行。

1.2 硬件连接

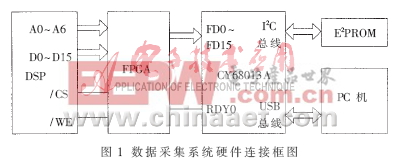

参考文献[1]对各种数据采集系统进行了分析比较,并指出USB总线为数据采集卡与PC机较理想的接口,因此选用CY68013A作为USB接口芯片。采用1片FPGA进行DSP与CY68013A之间数据格式的转换,CY68013A固件程序存放在E2PROM中,通过I2C总线连接,连接方式如图1所示。

其中,DSP除了输出16位数据总线之外,还引出7位地址线(A0~A6),用以区分不同的数据类型。FPGA须将DSP外部总线输出的数据格式转换为CY68013A外部GPIF可兼容的格式。

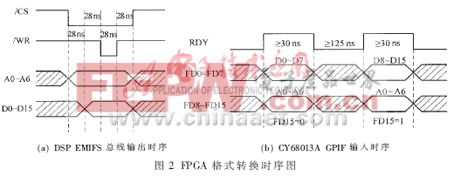

1.3 FPGA程序设计

CY68013A外部GPIF端口可作为数据输入端口的仅有16位(FD0~FD15),而DSP输出的信息数据一共有23位(16位数据线D0~D15和7位地址线A0~A6),故而需要将多出的7位地址信息嵌入到数据中去。将1个16位数据拆分成2个,每个数据中的低8位(FD0~FD7)用于存储原数据信息(D0~D7或D8~D15),高7位(FD8~FD14)存放地址类型信息(A0~A6),最高位(FD15)用于标识当前数据中FD0~FD7是原数据的D0~D7或是D8~D15,具体格式如图2(b)所示。CY68013A GPIF端口使用内部48 MHz时钟,根据参考文献[2],每个GPIF信号周期为20.83 ns,二者时钟不同步,FPGA为了与高速设备兼容,需要使用更高的时钟源。因此,为了保证GPIF能够采集到RDY信号,FPGA输出的信号至少需要保持1.5个GPIF信号周期。GPIF每次从外部读取数据存入FIFO需要6个状态,故而每个输出数据间隔应大于6个GPIF信号周期。以TI公司C55系列DSP为例,主频时钟144 MHz,与FPGA连接的为EMIFS外部总线,则FPGA转换信号时序如图2所示。其中,图2(a)为DSP EMIFS输出时序, 图2(b)为经FPGA转换后的CY68013A GPIF输入时序及数据格式。

考虑到DSP输出数据时钟可能较CY68013A GPIF采集时钟快,因而FPGA需要设计内置的FIFO存储器,用于缓存DSP输出的数据。

1.4 USB固件设计

由于CY68013A内置的8051内核时钟周期较慢,不适于高速传输,因而采集程序中仅使用8051进行初始化配置,而不干预数据传输过程。CY68013A通过外部GPIF读取数据存入FIFO中,FIFO满时通过USB传入PC机。采用Cypress公司提供的通用程序框架以及图形化GPIF设计工具,参照图2(b)的时序,编辑GPIF波形。USB总线选择传输大量数据时比较常用的Bulk传输模式,硬件配置程序采用Cypress公司提供的程序模板,参考文献[3]对该模板进行了详细说明,这里不再赘述,程序框架与参考文献[4、5]类似。

1.5 PC机接收程序

USB接口驱动程序可直接使用Cypress公司提供的ez-usb驱动。由于ez-usb驱动没有提供高级的文件操作IO方式,因而需要调用比较底层的DeviceIoControl函数来处理。考虑到Bulk传输方式完全是由主机端(PC机)发起读操作,从机端(采集板)只能被动地等待,而当CY68013A内置的FIFO写满之后,如果主机不能及时地发起读操作,则FIFO不再接收数据写入操作,因而会有少量的数据丢失。对于底层协议栈调试,这种少量的数据丢失可能引起程序流程错误,是不能接受的。因此PC机端接收程序应采用多线程处理方式,将接收USB数据的工作列为单独的线程,并将其优先级设置为实时性最高的THREAD_PRIORITY_TIME_CRITICAL,防止接收数据过程被系统中其他进程打断,以确保每次读操作能够及时发出。同时也要保证负责数据采集的PC机操作系统中同时运行的进程尽量少,关掉不必要的后台进程。

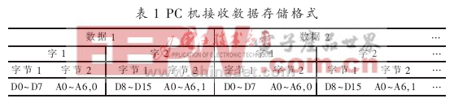

PC机接收到的数据先存入临时文件中,以备后续解析、仿真程序使用。临时文件以字(16 bit)为单位存储,每个数据用2个字来表示,低字节在前,与FPGA转换后的数据格式一致,如表1所示。

2 仿真系统

仿真系统使用采集系统采集到的数据,再现通信终端中的协议栈运行状态,便于开发者随时检查程序错误,对程序进行调试。

2.1 系统框架

要想再现底层协议栈运行状态,除了保证协议栈整体输入、输出一致外,最大的难度在于系统的定时,要能够准确再现各种事件的发生时刻。基于软件无线电技术的数字通信系统大都采用过采样方式,AD/DA速率都比较高而且稳定,因而底层协议栈也大多以AD/DA的输入、输出中断作为系统定时。当通信终端作为接收机时,底层协议栈需要以AD采样数据作为其他部分(信道估计与均衡、解调、信道解码等)的驱动数据;作为发射机时,DA输出数据是底层协议栈的最终输出结果,需要仿真程序进行验证。故而仿真程序可以采用AD/DA中断来划分程序运行的最小时间片,其他各种事件的发生都通过中断个数来计时,仿真程序通过判断AD/DA数据的个数调用各程序函数来再现底层协议栈运行状况及数据流向。这样就可以在不增加开销的情况下,尽最大可能保证仿真程序与实际DSP中运行的协议栈一致,方便再现问题。

评论