基于FPGA的PROFIBUS-DP总线光电收发器设计

O 引言

PROFIlBUS-DP现场总线以其高速、低成本等优点而广泛应用于制造业自动化、流程工业自动化和楼宇自动化等行业,它的物理层数据传输依赖RS-485接口。RS-485接口是一种工业领域内广泛使用的串行通信接口,可采用“差分”方式在屏蔽双绞线中传输信号,因而具有较好的抗共模干扰能力,通信距离可达千米。PROFIBUSDP总线信号也可使用屏蔽双绞线传输,数据速率为9.6 kbps时的理论传输距离为1200米,波特率为12:Mbps时的理论传输距离为100米。但是,由于工业现场情况错综复杂,各种干扰相互叠加,且RS-485标准规定单段网络最多可支持32个节点(标准负载),因此,有必要使用一种中继设备来将信号更准确、更完整地传输到远端设备。而光纤和其他传输介质相比具有宽频、低损耗、屏蔽电磁辐射、重量轻等优点,因此,用光电收发器实现两线制DP(RS-485)差分信号数据与光信号之间的转换,能够有效的提高信号传输距离和传输质量,从而提高系统的可靠性与稳定性。

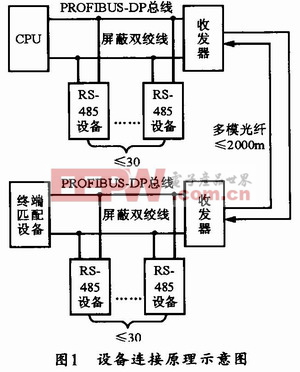

1 光电收发模块的配置原理

本光电收发模块的使用配置如图1所示。从物理层来说,原来的一个网段被光纤分成两段,此时。收发器应视为相应段的总线末端,因此,在收发器中默认内置了有终端匹配电阻,以使负载端输入阻抗与传输线的特征阻抗相匹配,从而达到消除负载端信号反射的目的。每一个光电收发器在电气性能上都占一个节点,因此,每段总线上最多可以带30个标准RS-485负载设备。

2 总体设计方案

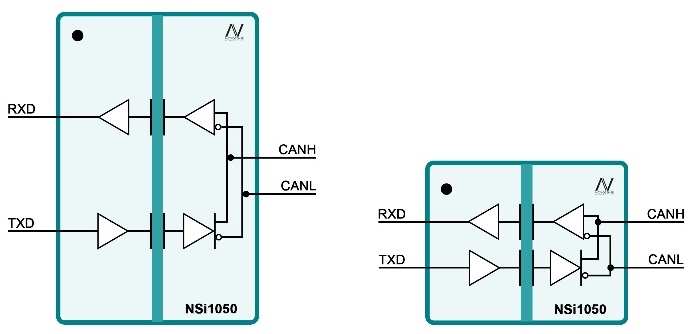

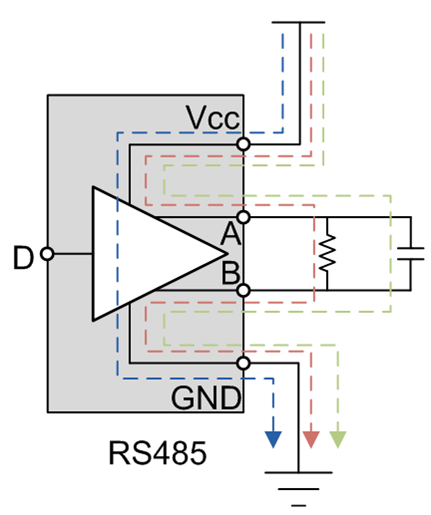

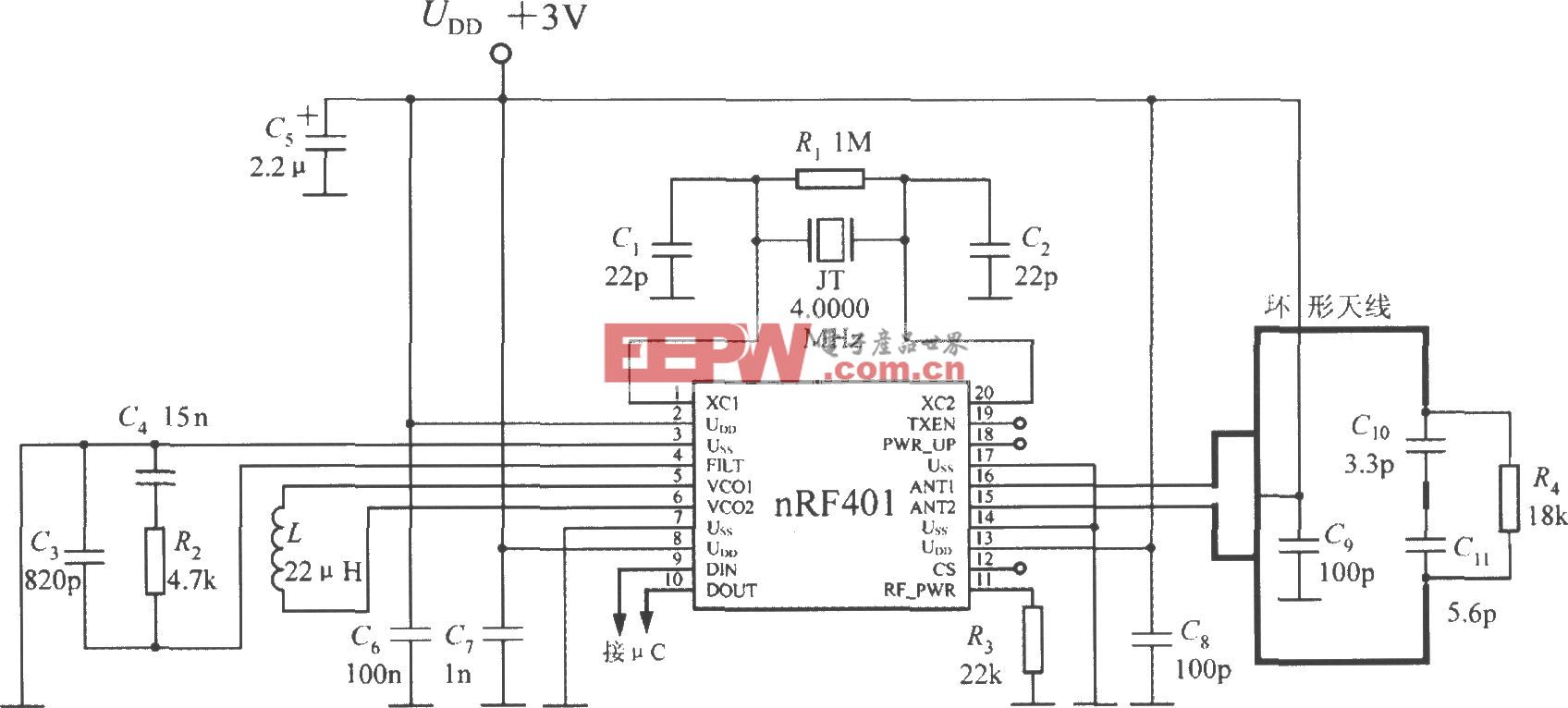

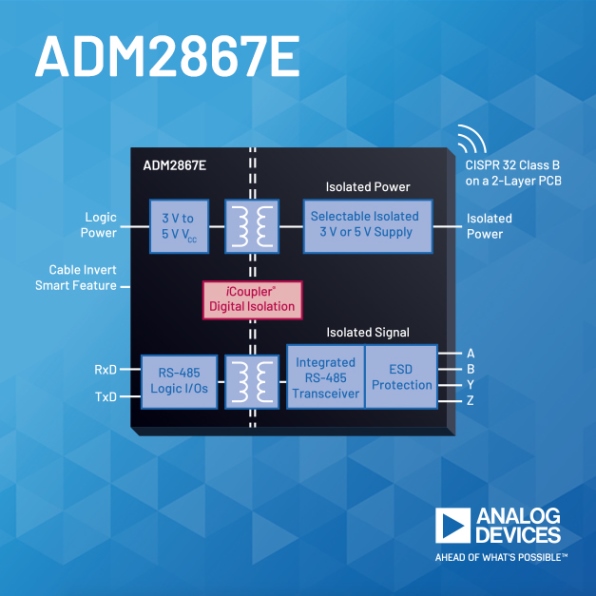

图2所示是光电收发器的硬件结构框图。该设计方案整体上由DP总线数据收发部分、光纤数据收发部分和数据传输方向控制部分组成。 FPGA作为主控制器负责控制数据传输的方向、检测波特率和数据交换功能。其中电源部分采用隔离的DC/DC来减少外部电路的影响。电端DP总线的RS-485收发器可选用SN75HVD06D,该芯片可支持10 Mbps数据速率;而光端的数据接收器和发送器则可选择AVAGO公司的光发送器HFBR-14x4Z和光接收器HFBR-24x2Z,它们在50mA电流驱动下,其62.5/125μm的多模光纤传输距离可达2 km。FPGA芯片选用ALTERA公司的Cvclone系列芯片EPlC3T144C8N,该芯片有2910个LE单兀、1个PLL和144个IO引脚,且性价比较高。

评论