一种高可靠性的计算机与FPGA串行通信的实现

摘要:主要介绍以FPGA为硬件平台的下位机与计算机(上位机)进行串行通信,将串口功能集成到单片FPGA内,运行中波特率可调,经过适当的倍、分频实现了零误差的波特率发生器,提高了数据传输的可靠性。上位机上编写VB程序负责主设备的发送命令并接收显示来自FPGA回发的数据,实验结果表明通信可行,可靠性高。

关键词:FPGA;串行通信;VB;可靠性

串行通信广泛应用于数字通信和工业控制领域,传统的专用串口通信芯片接口复杂,体积较大,随着微电子技术的发展,FPGA的等效门数迅速增加,可以完全将串口功能集成在单片FPGA内,减少了外围电路的体积,降低了设计的复杂性,同时也提高通信的可靠性。

1 串行通信的原理

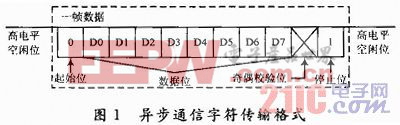

串行通信是指通信的发送和接收方之间数据信息的传输是在单根数据线上完成,以每次一个二进制的0或1为最小单位逐位进行传输,本文采用异步的全双工通信方式,数据传输是以字符为单位,如图1所示为异步通信的帧格式。

其中,一帧数据包括起始位、数据位、校验位和停止位。线路空闲状态下,发送和接收端均保持高电平;通信开始时,通信一方发送一个起始位(低电平),表示通信的开始,紧接着发送有效的数据位,通常约定的数据位有5,6,7或者8位,根据用户需要进行设定,然后发送校验位,这里选用偶校验,最后发送停止位,可以是1,1.5或2位不等,用户自行约定即可。本文选用8位数据位、偶校验、1位停止位,可以实现所有字符的收、发。

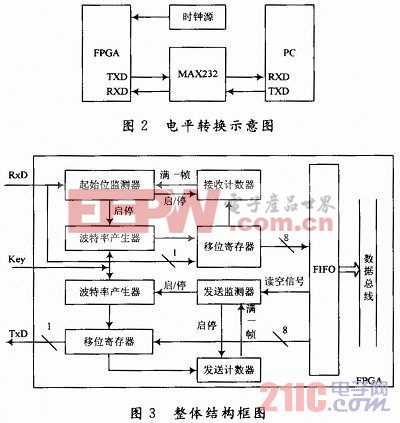

串行通信传送数据是按位顺序进行,最少只需要一根传输线即可完成,要实现全双工的通信共需要2根数据线和1根接地线即可,通信双方可以在同一时刻进行发送和接收的操作。本文采用的是RS 232C串行接口标准,是目前PC机与通信工业中应用最广泛的一种串行接口。但计算机的串口是用正负电压来表示逻辑状态,与FPGA电路板上以高低电平表示的逻辑状态的标准不同。因此,为了能够同计算机进行通信,必须在两者之间进行电平的逻辑关系转换,本文采用集成电路芯片MAX232来完成两种电平的双向转换。如图2所示。

评论