安全认证系统中嵌入USB接口技术

USB(Universal Serial Bus)通用串行总线是计算机与其外围设备通信的一种总线标准,是近年来应用在PC领域的新型接口技术。它的热拔插、即插即用、连接简单、高带宽、可总线供电等优点几乎使其成为目前计算机外设的首选通信接口。世界上几乎所有硬件厂商都生产实现USB协议的芯片。厂商们本着通用性原则,有的在芯片中嵌入了通用微处理器,如CYPRESS公司CY7C6××××系列和INTEL930××系列嵌入了8051系列微控制器;有的则提供了各种常用的与微处理器接口的方案,如NATIONAL SEMICONDUCTOR公司的USBN960× 系列提供了多路与非多路的8位并行接口、DMA并行接口及微波接口;PHILIPS公司的PDIUSBD11提供了I2C总线接口;三星公司研制的USB功能控制器则具有8位并行微处理器接口,并能以同步或者异步方式工作,这为使用USB协议作为通信接口提供了极大的方便。然而,将USB功能嵌入到一种用于安全认证的处理系统中,则存在无法与处理器直接接口的问题。本文探讨了USB功能模块和处理器接口技术,并从其基本应用角度出发,给出了相应的软件流程。具有USB接口的安全认证系统使用简单、便于携带、通信速度快。

本文引用地址:https://www.eepw.com.cn/article/152564.htm1 USB功能模块

USB功能模块是基于微处理器应用实现USB协议的模块。集成有低速USB收发器,配置有3个基于FIFO的端点、1个控制端点(8字节)、2个可配置传输方向的中断端点(8字节)。每个端点都配置有相应的控制与状态寄存器,带有一个8 位微处理器并行接口,可工作在同步或异步方式。

USB功能模块的操作对用户来说是完全透明的。包的译码、数据传输到FIFO、从FIFO发送数据和USB包的装配都是自动完成的。当接收到一个正确数据包或发送成功一个数据包,即向MCU发出中断请求,请求将数据取走或装入下一个要发送的数据包。端点FIFO对USB来说是缓存单元,对MCU来说是一个I/O端口。微处理器通过访问USB寄存器来控制USB模块的操作。

1.1 端点0控制/状态寄存器

D0:OUT_PKT_RDY FIFO装有一个有效数据包,USB将其置1,产生中断,MCU写D6为1,清除D0。

D1:IN_PKY_RDY USB成功发送完一个数据包,清D1时产生中断。

D2:SENT_STALL 控制交换因违反协议而终止,USB置D2,产生中断。

D3:DATA_END MCU装了最后一个数据包到FIFO,置D3,与此同时,置D1。MCU卸载完FIFO最后一个数据包,清D0,置D3。对于0长度的数据相,MCU卸载完SETUP数据包之后,清D0=0,置 D3=1。USB清D3时产生中断。

D4:SETUP_END 在DATA_END(D3)置位之前,控制传输结束,USB置D4,产生中断。

D5:SEND_STALL 如果译码为一个无效的令牌,MCU置D5,与此同时,清D0,USB发STALL给当前的控制传输,MCU写D5=0,结束STALL条件。

D6:SERVICED_OUT_PKY_RDY MCU写D6=1以清除D0。

D7:SERVICED_SETUP_END MCU写D7=1以清除D4。

1.2 USB功能模块的访问时序

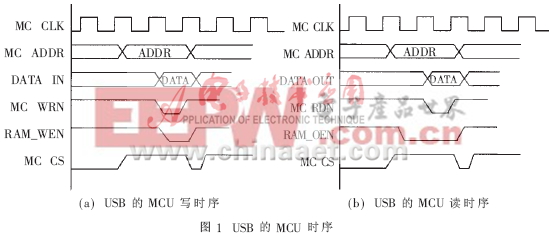

USB功能模块的I/O接口可工作在同步或异步方式,本文采用同步方式。其对MCU访问的读写时序要求如图1(a)、(b)所示。

写时序:地址至少要维持两个时钟周期,并且要先于数据一个有效时钟周期,以便将FIFO的写指针选通至RAM写地址端口。当写信号有效时,存储器写使能信号有效,写之后一个时钟周期FIFO指针刷新。地址有效时,片选高有效。

读时序:一旦地址有效,存储器输出使能有效。地址至少维持两个时钟周期,前一个周期将FIFO的读指针选通至RAM的读地址端口,因此数据比地址晚一个时钟周期出现在数据总线上。当读信号有效时,MCU将总线上的数据读走,与此同时,FIFO的指针刷新。地址有效时,片选高有效。

系统中采用了具有加解密功能的处理器。处理器采用栈式结构,具有焦点聚合的低功耗内总线结构和超标量指令结构与多种寻址方式等特点,能高速高效地处理数据。嵌入有RSA和DES模块,能对发送和接收的数据进行实时RSA算法或三重DES算法的加密和解密。系统具有8位地址总线,16位数据位宽的并行接口,其I/O访问时序如图2所示。从图2可以看出,I/O访问在一个时钟周期内完成。

评论