PowerPC嵌入式系统中的以太网接口设计

l 引 言

PowerPC是1993年IBM,Apple和Motorola公司(其半导体部门现在分拆为Freescale公司)联盟的共同设计的。PowerPC技术以RISC(精简指令集计算机)为基础,该技术由IBM的POWER(性能优化的增强RISC)体系结构而来。因PowerPC芯片具有高性能和低功耗的特点,主要应用在嵌入式系统。MPC7410是新一代G4处理器,通过加入A1tiVec技术,处理能力达到4G FLOPS,而1.8V的低电压操作大大降低了芯片的功耗,提高了系统的稳定性。MPC7410内部主频最高为500 MHz,每个时钟周期最多可以执行8条指令,其中包括4条矢量运算(A1tiVec)指令和2条整型指令。系统采用MPC7410为核心处理器搭建嵌入式系统硬件平台。利用Tsi107芯片组的PCI接口连接以太网。网口是系统非常重要的通信接口,通常情况下操作系统映像的下载以及与外界的通信都是通过以太网口进行的。文中介绍了以太网接口硬件设计和VxWorks BSP的开发。

2 系统结构概述

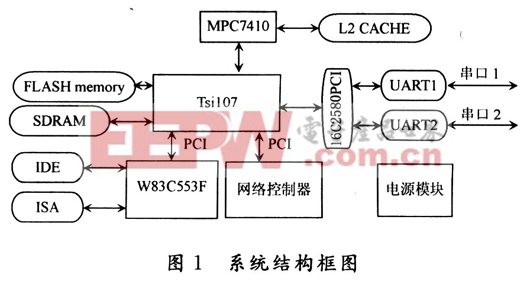

整个系统结构框图如图1所示。

在系统中使用了Motorola公司的RISC处理器Pow―erPC7410作为核心处理器,该处理器具有高性能和低功耗的特点,外接一个2 MB L2作为二级缓存,以提高运算速度。以Tundra公司为PowerPC专门设计的桥芯片/存储器控制器Tsil07作为北桥芯片,利用60X总线和MPC7410相接,用以把60X总线信号转化为PCI总线信号,并管理FLASH和SDRAM。此设计充分利用60X总线高数据传输速率和优秀的连接性能,发挥了MPC7410的高可靠性和强大的处理能力,使该硬件平台具有很高的性能。

3 Tsil07的PCI接口

Tsil07的PCI接口与PCI 2.1规范兼容。使用一个32位地址/数据复用线。在PCI总线和处理器或本地memory之间提供内部缓冲。处理器读和写操作分别有1个32 B缓冲,memory操作具有2个32 B读缓冲和2个32 B写缓冲。PCI总线使用中央仲裁方式,每一个master都有它自己的请求(REQ)和获得(GNT)信号。可通过一个简单的请求――获得握手获得总线的控制权。仲裁在前一个访问时发生,故不会占用PCI总线的周期。

Tsil07为自身和另外最多5个PCI总线master提供总线仲裁逻辑,可通过设置PCI仲裁控制寄存器(PACR)的位15决定是否使能(置为1)或禁止(置为O)片内PCI仲裁器。在复位信号(HRESET)为高时采集SDMA9以确定片内PCI仲裁器被使能(低)或禁止(高)。

片内PCI仲裁器使用一个可编程的、两级、round―robin仲裁算数逻辑,5个外部master的每一个,加上Tsi107使用PACR中的适当位被编成2个优先级,高或低。低优先级组在高优先级组中共同占用一个总线请求传输通道。系统中如果有N个高优先级设备和M个低优先级设备,则每一个高优先级设备最少会得到![]() 总线传输,每个低优先级的设备最少会得到

总线传输,每个低优先级的设备最少会得到![]() 总线传输。

总线传输。

4 地址映射关系

根据Tsi107在电路中所起的作用它的工作方式可以分为2种,host mode和agent mode。在host mode,Pow―erPC是整个板子的主CPU,Tsi107管理整个系统的Memory和PCI总线。在agent mode,PowerPC系统是一个PCI设备,Tsi107负责和PCI主桥通信,管理这个PCI设备局部的memory。整个PowerPC系统受PCI主桥管理。在本系统中Tsi107工作在host mode。Tsil07在host mode时可采用2种地址映射方式,map A和map B。在复位时通过地址映射配置引脚SDBA0选择地址映射方式。如果Tsi107工作在host mode并且SDBA0上拉,则Tsil07使用map B。建议不使用map A,使用map B时,PowerPC和PCI的地址映射关系如表1所示。

评论