PowerPC嵌入式系统中的以太网接口设计

5 网口部分设计

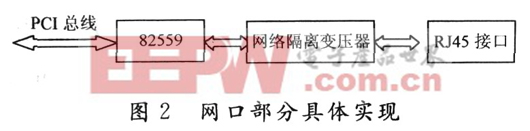

网口部分的设计基于芯片组Tsil07控制的PCI总线,基本框图如图2。

网口部分主要由Intel 82559,网络隔离变压器和RJ45接口3部分组成。82559是一个高集成度、高性能、低功耗的10/100 Mb/s快速以太网控制器,符合LON设计规范。物理尺寸只有15 mm×15 mm,是一款高性价比芯片。82559有完整的PCI接口,既可作主设备又可作从设备,在系统上电对其进行配置时只能作为从设备,正常工作后可作为主设备。32位的PCI控制器使82559在PCI总线上执行高速的数据传输。并且PCI控制器可处理通信任务,因而减轻CPU的负担。82559包含一个传输FIFO和一个接收FIFO,大小各为3 kB,在等待总线传输时可防止数据的流失。这将使82559利用最小的帧间距传送数据。82559可工作在全双工和半双工模式。82559连接一个E2PROM,E2PROM为硬件和软件提供上电初始化。在82559芯片上集成了MAC(介质访问子层)和PHY(物理层)的功能,通过片上的命令和状态寄存器经由PCI总线和PowerPC通信。H1102是一个网络隔离变压器,82559通过网络隔离变压器驱动刚45网线接口,用来支持10/100BASE―T,实现与外界通信。

6 以太网的VxWorks BSP的开发

BSP即Board Support Package,板级支持包,是对目标系统的底层支持软件。对于具体的硬件平台,与硬件相关的代码都被封装在BSP中,由BSP向上提供虚拟的硬件平台,BSP与操作系统通过定义好的接口进行交互。BSP是所有与硬件相关的代码体的集合,是介于底层硬件和上层操作系统之间的一层,主要目的是为了支持操作系统,使之能够更好地运行于硬件系统。以下介绍了网口的VxWorks BSP的开发方法。

6.1 Tsil07的PCI接口的寄存器初始化

对Tsil07的PCI接口的寄存器初始化主要是对PCI命令寄存器,PCI状态寄存器,PCI仲裁控制寄存器等和PCI相关的寄存器设置。因用户手册上对各寄存器的参数进行了详细的说明,在此将不再赘述。

Tsil07中的32位配置寄存器地址是0x8000_00nn,nn是寄存器的相对偏移地址。对配置寄存器的访问采用间接方式,将配置寄存器的地址写到CONFIG_ADDR端口,则配置寄存器的内容将在CONFIG_DATA端口获得。CONFIG_ADDR端口的地址为:OxFEC0_0000~OXFEDF_FFFC,CONFIG_DATA端口的地址为0xFEE0_0000~0xFEEF_FFFF。

6.2 82559的PCI接口的寄存器初始化

对Tsil07的PCI接口的寄存器初始化包括对PCI命令寄存器,PCI状态寄存器,Cache行大小(CLS)寄存器等寄存器的设置,以便能够找到PCI设备82559,使Power―PC能够对该设备进行访问。

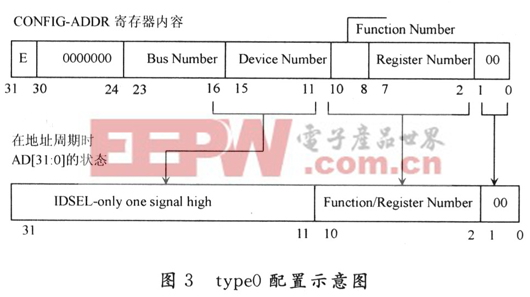

PCI定义了3个地址空间:PCI memory空间,PCII/O空间和PCI配置空间。PCI memory空间,PCI I/O空间采用直接访问。PCI支持2种类型的配置访问,typeO和type 1。AD[31:O]信号表示地址时根据配置访问的类型使用不同的形式,地址的低两位表明配置访问的类型――type O(AD[1:O]=ObOO)或type 1(AD[1:O]=Ob01)。2种地址形式都表明了一个具体的设备和该设备的一个具体的配置寄存器。typel 0用于在本地PCI总线上选择一个设备,type 1通过一个PCI―to―PCI桥传递配置请求到另一个PCI总线。系统采用type O配置,如图3所示。

为访问配置空间,必须向CONFIG_ADDR寄存器写入一个32位的值,用于定义目标PCI总线、该总线上的目标设备和设备中要访问的配置寄存器。对CONFIG_DATA寄存器的一个读或写操作将使主桥将该访问转化为一个PCI配置周期(CONFIG_ADDR中的使能位被设置并且设备编号不是0b1_1111)。

对于map B,处理器可在地址空间0xFEC0_0000~0xFEDF_FFFF中使用任何地址访问CONFIG_ADDR寄存器。尽管系统可以使用0xFEC0_0000~OxFEDF_FFFF中的任何地址,但一般使用地址0xFEC0_0CF8。为简化CONFIG_ADDR的地址通常被称为CF8。处理器可在地址空间0xFEE0_0000~0xFEEF_FFFF中的任何地址访问CONFIG_DATA寄存器。最常用的地址为0xFEE0_OCFC~0xFEE0_0CFF。为简化起见,一般指为CFC。

对于type O配置,Tsi107把CONFIG_ADDR寄存器的设备编号转化为惟一的IDSEL信号,它们之间有一一对应的关系。功能编号和寄存器编号将不加改变的复制到AD[10:2],AD[1:O]在type O配置时为0b00。

6.3 中断的实现

Tsil07的EPIC(可编程中断控制单元)支持5个外部中断。IRQ[O:4]信号代表了外部中断,它们被5个IRQ向量/优先级寄存器(IVPRO―IVPR4)控制和初始化。外部中断可被设置为电平或边沿触发。软件通过对向量/优先级寄存器的写操作为每一个中断源设置优先级,优先级的值在O~15之间,15最高。EPIC单元通过丽向处理器核申请中断。当处理器通过对EPIC单元中的中断响应寄存器(IACK)进行读操作以响应中断请求时,EPIC返回一个8位的中断向量到处理器,然后处理器处理该中断。处理器对EPIC单元的结束中断(EOI)寄存器进行写操作时,中断处理完成。

对EPIC的初始化主要是设置各中断源的优先级和中断向量的设置。包括对特征报告寄存器(FRR)、全局配置寄存器(GCR)、伪向量寄存器(SVR)、外部和内部中断寄存器等的设置。

7 结 语

搭建以MPC7410为核心处理器的嵌入式系统硬件平台,阐述以太网接口硬件设计和VxWorks BSP的设计方法,使以太网接口在系统中能正常通信。

评论