基于嵌入式微处理器和FPGA的高精度测频设计

引 言

本文引用地址:https://www.eepw.com.cn/article/152401.htm本课题来源于一个无纸记录仪的项目。在该项目中要求无纸记录仪中有一路通道将工业现场采集到的频率信号测量并显示出来。

传统的测频系统大多采用单片机加逻辑器件构成,而这类测频系统存在测频速度慢、准确度低、可靠性差的缺点,故而使测量仪表达不到工业现场的要求。鉴于此,本文设计了一种基于嵌入式微处理器SEP 3203和FPGA的测频系统。将嵌入式微处理器灵活的控制功能与FPGA的设计灵活、高速和高可靠性的特点有机结合,从而达到工业现场的实时测量要求,而且该测频系统具有可重构性。

2 测频原理

常用的直接测频方法主要有测频法和测周期法2种。测频法就是在确定的闸门时间tw内,记录被测信号的变化周期数(或脉冲个数)Nχ,被测信号的频率为fχ=Nχ/tw。测周期法需要有标准信号的频率fs,在待测信号的一个周期内tχ,记录标准频率的周期数Ns,被测信号的频率为fχ=fs/Ns。这2种方法的计数值会产生±1个字的误差,并且测试精度与计数器中记录的数值Nχ或Ns有关。为了保证测试精度,一般对于低频信号采用测周期法,对于高频信号采用测频法,这样测试时很不方便,所以人们提出了等精度测频的方法。

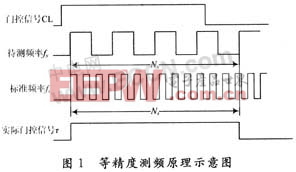

等精度测频方法是在直接测频方法的基础上发展起来的,他的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,消除了对被测信号计数所产生±1个字的误差,达到了在整个测试频段内保持等精度测量。其测频原理如图1所示。

在测量过程中,有2个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成1次测量过程。从而实现了实际门控信号与被测信号的同步,进而消除对被测信号计数产生的一个脉冲的误差。

设在1次实际闸门时间τ中计数器对被测信号的计数值为Nχ,对标准信号的计数值为Ns。标准信号的频率为fs,则被测信号的频率为:

fχ=(Nχ/Ns)×fs (1)

3 误差分析

由式(1)可知,若忽略标频的误差,则等精度测频可能产生的相对误差为:

δ=(fχ-fe/fe)×100% (2)

其中,fe为被测信号频率的准确值。在测量中,由于fχ计数的起停时间都是由该信号的上升沿触发的,在闸门时间τ内对fχ的计数Nχ无误差(τ=Nχtχ);对fs的计数Ns最多相差1个数的误差,即│△Ns│≤1,其测量频率为:

fe=[Nχ/(Ns+△Ns)]/fs (3)

将式(1)和式(3)代入式(2),并整理得:

δ=│△Ns│/Ns≤1/Ns-1/(τ×fs) (4)

由上式可以看出:测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关,即实现了整个测试频段的等精度测量。闸门时间越长,标准频率越高,测频的相对误差就越小。标准频率可由稳定度好、精度高的高频晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。

4设计框图及实现

(1)前级电路

即首先对待测信号进行处理使其达到与后级电路相兼容的脉冲信号。原理框图如图2所示。具体实现电路如图3所示。

第一级电路是由开关三极管组成的零偏置放大电路,以保证放大电路具有良好的高频响应,当输入信号为零或负电压时,三极管工作在截止状态,输出为高电平,当输入为正电压时,三极管工作在饱和状态(导通),输出电压随输入电压上升而下降。零偏置放大电路把如正弦波样的正负交替波形变换成单向脉冲,这使得该电路可以测量任意方波信号、正弦波信号、锯齿波信号、三角波信号等频率。

第二级采用的是施密特非门触发器CC74HC14,是对放大器输出的信号进行整形,使其输出的信号成为与后级电路相兼容的脉冲信号。

(2)后级电路

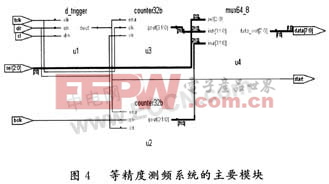

图4为测频系统的主要模块。图4中各模块用硬件描述语言Verilog HDL描述,通过EDA工具(ModelSim,Synplify,QuartusⅡ)进行编译、仿真、延时分析、管脚调整、综合等步骤,最后烧录到FPGA芯片中。将芯片与被测信号的放大整形模块等外围电路相连接,通过调试便完成了整个设计。

评论