基于DSP的实时图像处理系统

引言

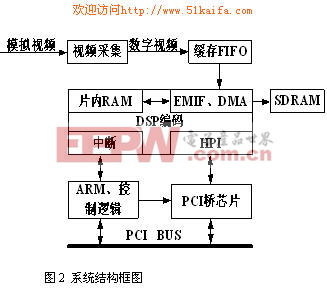

本文引用地址:https://www.eepw.com.cn/article/152273.htm本文设计了基于TMS320C6000系列DSP的MPEG-4编码器。将摄像头获取的图像以MPEG-4标准进行实时压缩并通过VGA实时显示,同时把压缩好的数据通过PCI总线传输给ARM控制器,经由ARM根据实际的需要进行视频数据的网络传输。

MPEG-4 是一种开放性标准,其中许多部分都没有规定,可以加入一些新的算法,因此采用通用DSP 能够随时更新算法、优化算法,使得编码效率更高。由于MPEG-4 编码算法复杂,需要存储的数据量大,无论是存储空间分配、数据传输还是运算速度对DSP来说都是挑战。

C6000系列DSP是TI公司生产的高档DSP。这一系列DSP都是基VelociTITM构架的VLIW DSP,它在每个周期可以执行八条32bit 的指令, 具有高达200MHZ的CPU,从而使得其运算能力达到1600MIPS。而6416在600MHz主频下,只利用50%的运算能力就可以同时进行单通道MPEG-4视频编码、单通道MPEG-4视频解码和单通道MPEG-2视频编码的处理。同时其对外接口灵活、开发工具齐全,被大多数嵌入式图像实时压缩系统所采用。因此本系统采用TI公司TMS320C6416芯片为核心处理器。

1.TMS320C6416的结构及特点

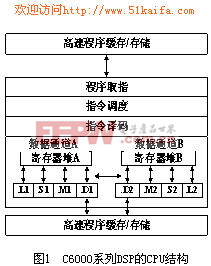

DSP的CPU结构如图1所示,它具有两个通道,每个通道具有4个功能单元(1个乘法器和3个算术逻辑单元),16个32位通用寄存器,每个通道的功能单元可以随意访问本通道的寄存器。CPU还有两个交叉单元,通过它们,一个通道的功能单元可以访问另一个通道的寄存器。另外, CPU还具有256 bit宽的数据和程序通道,可以使程序存储器在每个时钟周期提供8条并行执行指令。这种CPU结构是DSP具有VLIW结构的最基本条件。此DSP的存储空间映射为内部存储器、内部外设及扩展存储器。其中内部存储器由64KB内部程序存储器和数据存储器构成,内部程序存储器可以映射到CPU地址空间或者作为Cache操作。内部和外部数据存储器均可通过CPU、DMA或HPI(Host Interface)方式访问,HPI接口使上位机可以访问DSP的存储空间。

2.系统硬件设计

本系统主要分为三部分,分别是视频采集模块、视频的MPEG-4编码模块和视频传输模块,其结构框图如图2所示。

评论