基于DDS+PLL高性能频率合成器的设计与实现

摘要:结合DDS+PLL技术,采用DDS芯片AD9851和集成锁相芯片ADF4113完成了GSM 1 800 MHz系统中高性能频率合成器的设计与实现。详细介绍系统中核心芯片的性能、结构及使用方法,并运用ADS和ADISimPLL软件对设计方案进行仿真和优化,特别是滤波器的选择与设计。测试结果表明,该频率合成器具有高稳定度、高分辨率、低相位噪声的特点,达到了设计指标要求。

频率合成器是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率合成技术三种基本频率合成方法。直接频率合成技术原理简单,易于实现,频率转换时间短,但是频率范围受限,且输出频谱质量差。锁相频率合成技术(PLL)具有输出频带宽、工作频率高、频谱质量好的优点,但是频率分辨率和频率转换速度却很低。直接式数字频率合成技术(DDS)的频率分辨率高、频率转换时间快、频率稳定度高、相位噪声低,但目前尚不能做到宽带,频谱纯度也不如PLL。低相位噪声、高纯频谱、高速捷变和高输出频段的频率合成器已成为频率合成发展的主要趋势,传统的单一合成方式很难兼顾上述各项性能指标,达到现代通信系统对频率合成器的要求。本文采用DDS和PLL相结合的方法,设计一个应用于(GSM 1 800 MHz系统中的频率合成器,其中输出频带为1 805~1 880 MHz,分辨率为200 kHz,相位噪声为-80 dBc/Hz@1 kHz,频率误差为5 kHz,杂波抑制大于50 dB。

1 电路设计

1.1 设计原理

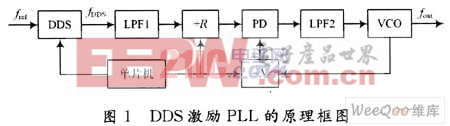

DDS直接激励PLL的频率合成技术,与单纯的PLL技术相比,作为参考源的DDS具有很高的频率分辨率,可以在不改变PLL分频比的情况下,提高PLL的频率分辨率,而且采用DDS激励PLL设计方法的电路结构简单,所用硬件少,通过合理设计环路滤波器可以较好地改善因PLL倍频作用而恶化的相位噪声。系统原理框图如图1所示。

图1中,fref是参考信号,一般由高稳定度的晶体振荡器产生,用于保证DDS各个部件的同步工作。fDDS取代原有的晶振作为锁相环(PLL)的激励源,其输出fDDS频率取决于频率控制字K。频率合成器的输出由VCO提供,PLL芯片中电荷泵的输出由低通滤波器(LPF2)产生,用于控制VCO的输出频率。DDS中K和PLL的分频比可以通过单片机中的控制程序加以改变,从而实现频率合成。

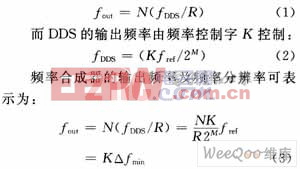

VCO输出信号频率与DDS输出信号频率之间的关系为:

式中:fref为DDS的时钟频率;K为DDS的频率控制字;M为DDS相位累加器字长;fref/2M为DDS的频率分辨率;△fmin为频率合成器输出信号的频率分辨率。由此可见,以DDS为激励源,只要相位累加器的字长取得足够大,频率合成器就能得到较高的频率分辨率。

评论