如何降低蓝牙装置的功耗

关键词: 智能安防;人脸检测;图像处理;DSP;FPGA

随着人们生活水平的提高以及安全防范意识的加强,视频监控系统得到了广泛应用。目前的监控多以PC机为主,只能起到简单的视频记录功能,同时需要配备专人监视屏幕。对于一些少有人出入的重要场所,通过人工方式对屏幕监控是一件麻烦的事情,而且PC机还需要配备大容量的硬盘来保存所有视频图像,硬盘使用量极大。针对这种情况,本文设计了一个无人值守的监控系统。系统在无人进入监视范围时不保存视频图像,当有人进入监视范围时才启动视频记录程序,同时自动快速捕获人脸,利用模式识别与图像处理技术对人脸特征进行分析,提取其特征量并与人脸库中的特征量进行匹配,判断是否为非法人员,如果是则进行报警,并通过网络提醒远程监控中心注意监视。对于平时很少有人出现的场合,利用该监控系统可以减少数据容量,减少监控人员,而且不会担心错过监视对象。本系统是在原有一代产品的基础上对硬件电路设计及软件算法上进行了改进。实践证明系统的反应速度、识别处理速度等都有了较大提高。

1 系统概述

摄像机在主控系统的控制下工作,在没有移动目标进入的情况下,摄像机的数据不存储。当拍摄到有人进入后,主控系统立即控制摄像机对非法进入指定区域的人体进行跟踪,并在跟踪过程当中对人脸定位并快速准确地获取其面部图像,同时启动录像功能;然后通过一系列的数字图像处理方法对面部图像进行分析、处理,确定是否为非法入侵,如果是则启动报警系统。利用多个这样的子系统可组成一个监控网络,各个子系统通过网络与监控中心连接。因各个子系统具有智能监控功能,所以监控中心只配备一个值守人员即可监控20个以上的监控点,大大减少了人员的使用。

2 系统硬件组成

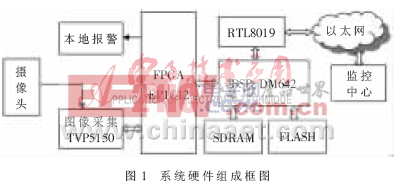

由于该系统处理的数据量较大,且要求实时性强,故采用DSP和FPGA相结合的方法,加上图像数据采集芯片以及存储芯片,构成核心图像处理单元。同时配备有本地报警模块、网络传输等,从而构成了一个完整的监控系统。系统组成框图如图1所示。与原有系统相比,本系统作了如下改进:把原来只作为数据缓冲处理的FPGA设计为主控芯片,控制数据的输入调理和输出报警,而把DSP解放出来,专门用作图像处理及传输。这样可以提高数据的处理速度,从而提高系统的反应速度。

2.1 系统主要芯片的选用

(1)图像采集芯片采用TVP5150。TVP5150是具备超低功耗、支持NTSC/PAL/SECAM等格式的高性能视频解码器。在正常工作时,它的功耗仅115 mW,通过设置内部寄存器,可以将模拟图像信号转换为YUV4:2:2格式的ITU-R BT.656数字信号,并直接送到DM642进行处理。

(2)为提供系统的快速反应能力,图像处理芯片的选择尤为关键,综合各方面的因素,DSP选用TI公司专用多媒体芯片TMS320DM642(简称“DM642”)。DM642基于C64x内核,可在720 MHz时钟频率下工作,每个指令周期可并行8条32 bit指令,能达到5 760 MIPS的峰值计算速度[6]。DM642采用了2级缓存结构(L1和L2),大大提高了程序的运行速度。片内64 bit的EMIF(External Memory Interface)接口可以与SDRAM、Flash等存储器进行无缝连接,极大地方便了大量数据的搬移。此外,DM642还拥有3个专用的视频端口(VP0~VP2),用于接收、处理视频和音频数据,系统功能扩展十分方便。此外,DM642自带的EMAC口以及从EMTF口扩展出来的ATA口,还为处理完成后产生的海量数据提供了存储通道[5]。DM642需要外加SDRAM(4 M64 bit),用于存放程序和缓存数字视频,以及FLASH(4 M8 bit),用于存放固化程序,以便进行ROM引导。

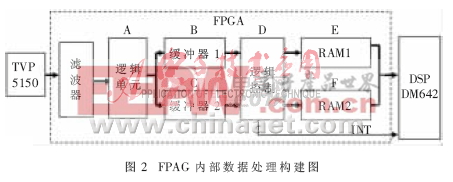

(3)FPGA负责实现系统的逻辑、输出控制以及内部缓存的时序控制。为实现图像的实时采集和处理,需要视频采集和图像处理并行工作。采集到的图像数据送到DSP前的缓存接口设计是关键,设计的优劣直接影响到系统的反应速度。要提高数据缓存读取速度,可利用FPGA内部资源构建高速双口RAM作为内部缓存,使数据帧处理交替进行,从而实现数据采集与处理同时进行,其内部结构如图2的虚线框内所示。采集到的数字视频信号先经过滤波处理,之后送入逻辑单元A,A负责产生时钟及数据逻辑控制。输入的视频数据信号在A的控制下,进入到缓冲器寄存器B和C,在控制单元D的控制下,送到双口RAM。为了实现实时图像采集和处理,使得FPGA对图像数据的缓冲和DSP对图像数据的读取同步进行,将RAM分成相等的2块,即RAM1和RAM2。在系统工作的过程中,一块用于缓冲图像数据,FPGA分类缓冲后的图像信号写入该存储区;另一块则由DSP用于对图像数据的读取,DSP可以直接对这个存储区的数据进行运算。该缓存结构的另一特点是FPGA和DSP对双口RAM的寻址是来回切换的。因为DSP读取RAM的速度大于FPGA写RAM的速度,所以切换信号仅由FPGA发出。当FPGA分类缓冲数据写满RAM1时,FPGA向DSP发出一个中断信号,此时DSP读取RAM1中的数据,同时FPGA的缓冲数据写入RAM2。当RAM2中数据写满时,FPGA再向DSP发出中断信号,DSP读取RAM2中的数据,同时FPGA的缓冲数据RAM1。如此交替实现图像数据读写同时进行,从而提高了数据处理的速度。

FPGA的选择较为关键,内部RAM的资源决定系统的反应速度。在原有一代系统中选用的FPGA资源较少,不足以存储一帧图像,因此数据的读写只能分块进行,需要控制逻辑较为复杂,同时也降低了整个系统的速度。对于一帧720×576的图像,共有414 720像素,每个像素8 bit,即共有414 KB的数据。因此可选用Altera公司的CycloneIII系列产品EP3C120。Cyclone III系列的FPGA采用65 nm技术,具有低功耗、低成本和高性能特点, EP3C120内部拥有120K个逻辑单元(LE),4 Mbit嵌入式存储器,288个嵌入式18×18乘法器,可以满足一帧图像的存储,在处理数据时可按照奇偶帧分别进行读写。

评论