基于Max+PlusⅡ平台的CMI编码器的设计方案

CMI码是传号反转码的简称,它是一种应用于PCM四次群和光纤传输系统中的常用线路码型,具有码变换设备简单、有较多的电平跃变,含有丰富的定时信息,便于时钟提取,有一定的纠错能力等优点。

本文引用地址:https://www.eepw.com.cn/article/151649.htm在高次脉冲编码调制终端设备中广泛应用作接口码型,在速率低于8 448 Kb/s的光纤数字传输系统中也被建议作为线路传输码型。

本文针对光纤通信传输码型的要求和CMI码的编码原理,介绍了一种以EPM系列7064芯片为硬件平台,以Max+PlusⅡ为软件平台,以VHDL为开发工具,适合于CPLD实现的CMI编码器的设计方案。

1 CMI码的编码规则

CMI编码规则如表1所示。

在CMI编码中,输入码字0直接输出01码型,较为简单。对于输入为1的码字,其输出CMI码字存在两种结果OO或11码,因而对输入1的状态必须记忆。同时,编码后的速率增加一倍。

2 CMI编码器的建模与实现

首先在原始时钟MUX_Clk的上升沿进行翻转得到二分频时钟Clk,周期为原始时钟的2倍。

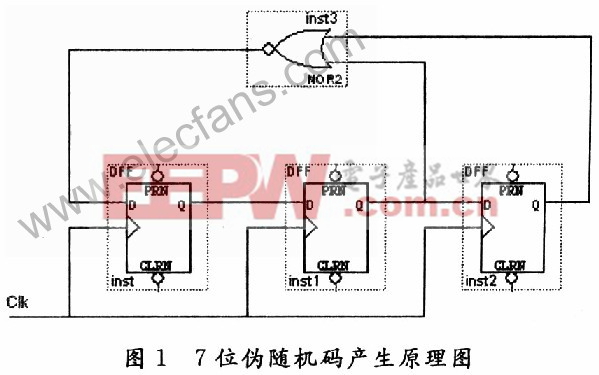

然后产生伪随机序列,由3个D触发器产生7位伪随机序列,序列产生原理如图1所示。

任何一个D触发器的输出都可以作为要产生的m序列,则序列以7为周期循环出现,在3个D触发器输出都为0时,语句m_buffer(2)=(m_bu-ffer(1)xor m_buffer(O))Or((not m_buffer(2))and(not m_buffer(1))and(not m_buffer(O))),可以使第一个D触发器在Clk上升沿到来时输出为1,从而避免陷入“000的死循环。

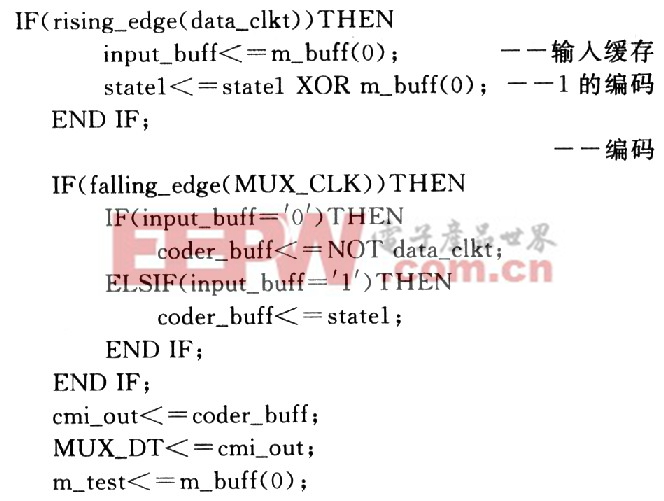

最后为“O”码、“1”码的编码:

“O”编码的实现:在原始时钟信号的下降沿对m序列进行检测,当其值为“0”时,将原始信号的二分频后的信号求非赋值给编码输出,即可实现对“O”进行“01”编码。

“1”编码的实现:在原始时钟信号的二分频信号的上升沿对m序列进行检测,如果其值为“1”,用表达式statel=statel X0R m_buff(O)对“1”的奇偶进行记录;在原始时钟的下降沿,将statel的值赋给编码输出即可实现对“1”的“00”,“11”交替编码。

评论