基于MPC860与STl6C654的串行通信设计

根据项目设计要求嵌入式处理器作为服务器,串行端口收发信息,经快速以太网接口实时发送到局域网。客户端将需要发送到串口的数据通过快速以太网接口经处理器转发到串口。因此,这是提出一种基于MPC860与STl6C654的串行通信设计方案。采用MPC860连接STl6C654。 MPC860是目前在网络与通信领域应用广泛的一款微处理器,其高速的PowerPC内核,连同集成的网络与通信外围设备,为用户提供一个建立高端通信系统的解决方案。STl6C654是一个带有收发各64字节、可扩展4路串行通道FIF0的扩展通用异步收发器,用于和高速调制解调器及需要快速处理数据时间的共享网络环境一起工作。

1 系统硬件设计

1.1 主要器件选型

1.1.1 MPC860型微处理器

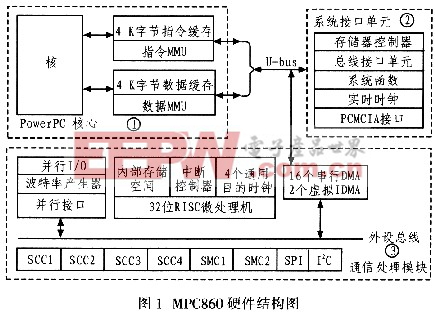

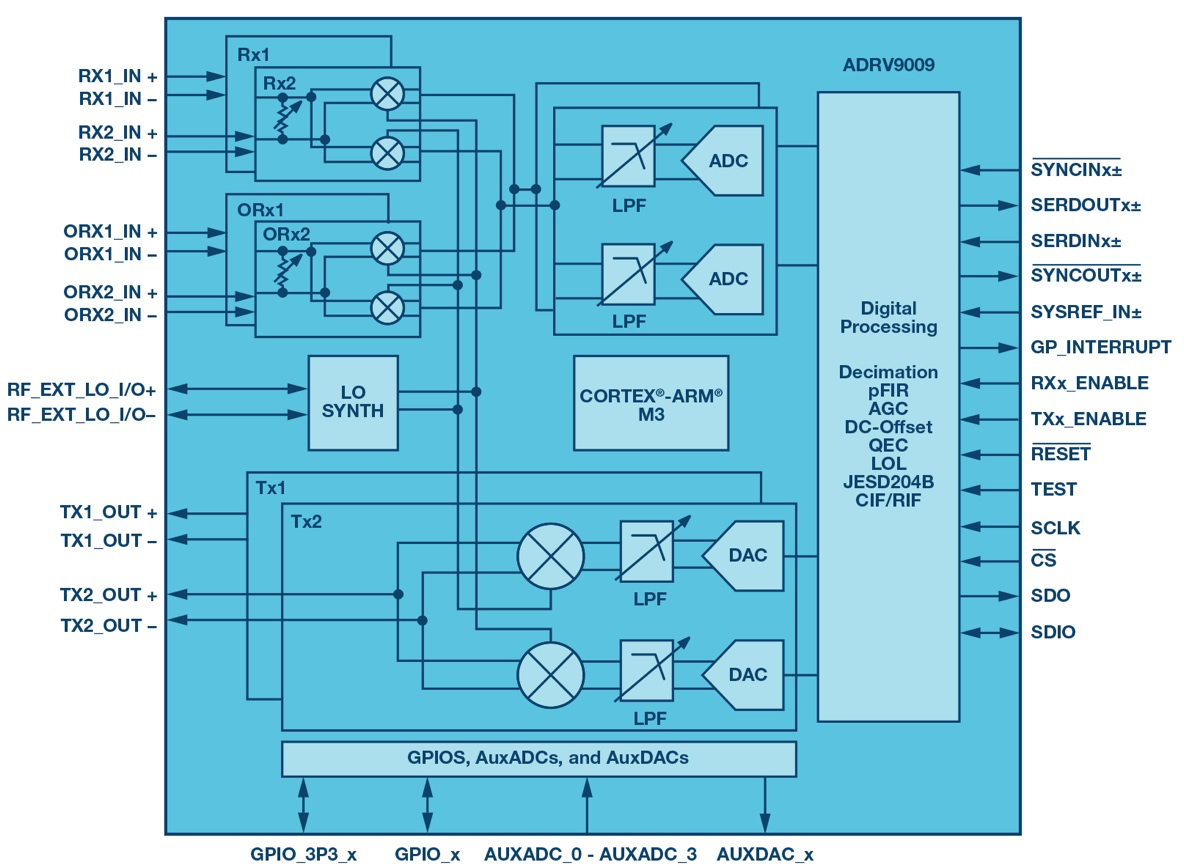

MPC860 PowerQIUCC(简称MPC860)内部集成了2个处理单元。一个处理单元是嵌入的PowerPC核(PowerPCCore),是主处理单元(CPU),是一个RISC芯片,通常编译后的程序指令都是由它执行;另一个处理单元是通信处理模块CPM(Communications Processor Module),内部集成有一个RISC微处理器,对各种常用的通信模块进行管理。通信处理模块内部集成有4个串行通信控制器SCC、2个串行管理控制器SMC、1个串行外围接口电路SPI和1个I2C接口。另外,还有一个系统接口单元SIU,主要功能是提供内外总线的接口及一些其他功能(如SIU中断)的管理等。本设计利用通信处理模块CPM强大功能,与STl6C654通信。MPC860硬件结构如图1所示。

1.1.2 STl6C654

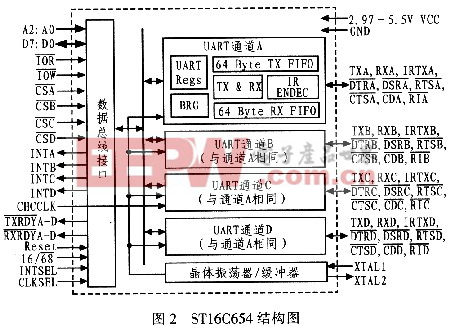

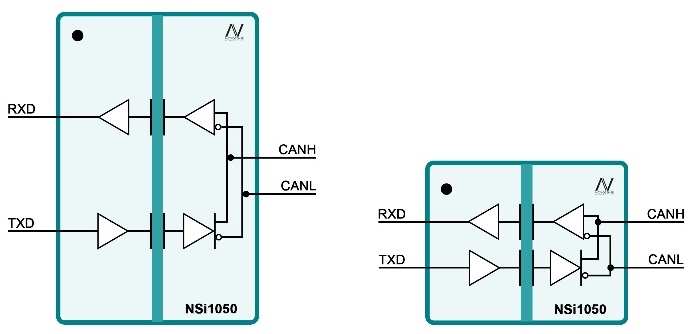

STl6C654是一个带有收发各64 Byte的FIF0的扩展通用异步收发器,自动软硬件流程控制,速率最高达到1.5 Mb/s(24 MHz时钟),支持16(Intel)/68(Motorola)总线接口类型。STl6C654结构图如图2所示。扩展的4路串口通道,每个通道有15个(64/68pin封装)或16个(100pin封装)内部寄存器,用来存放收发数据以及配置该串口的工作模式,需要在初始化时对各寄存器进行配置。工作模式有中断模式和定时查询模式,中断模式实时性能好,适合于紧急情况,中断次数多,中断任务切换频繁影响主要任务的运行;定时查询模式,由于STl6C654具有缓存,定时查询方式具备一般实时性,数据不丢失。

1.2 系统组成

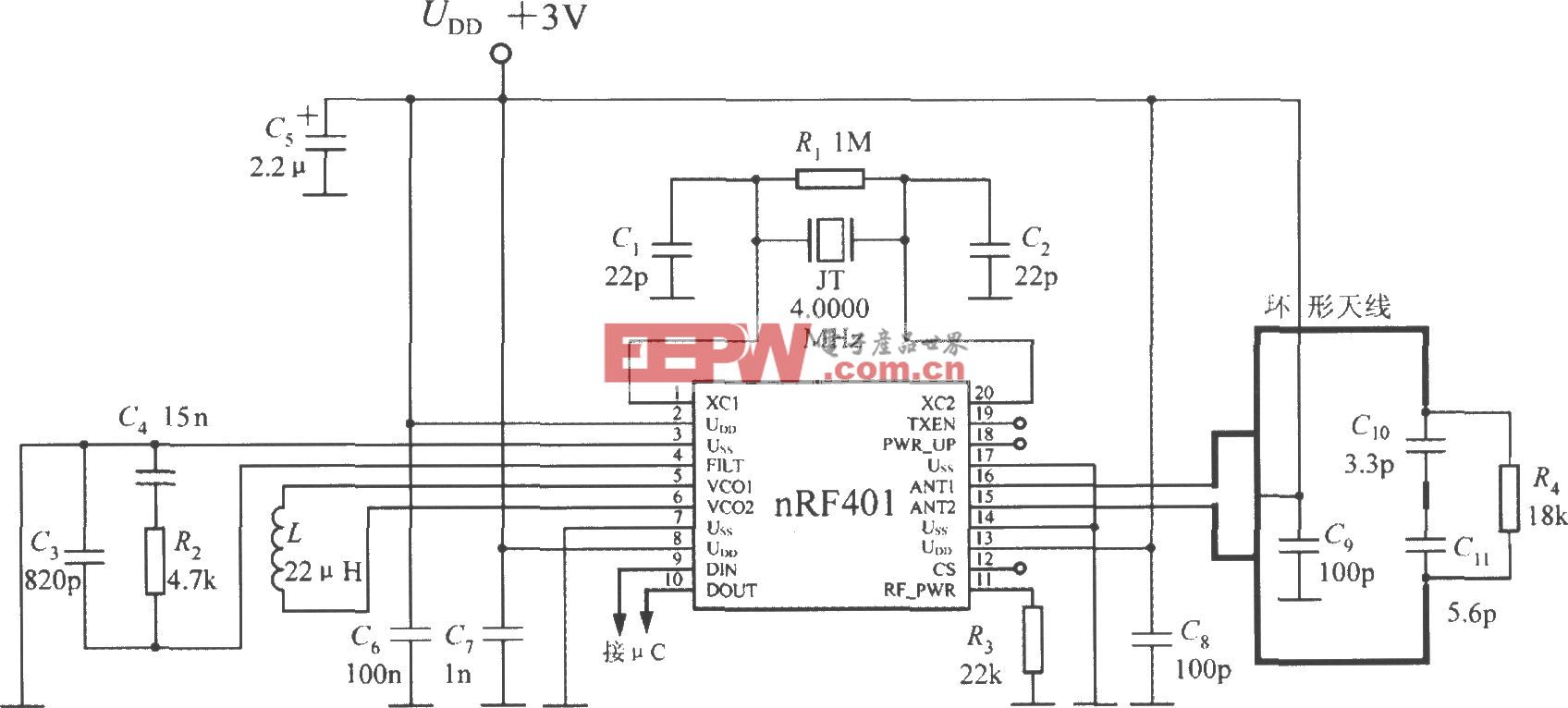

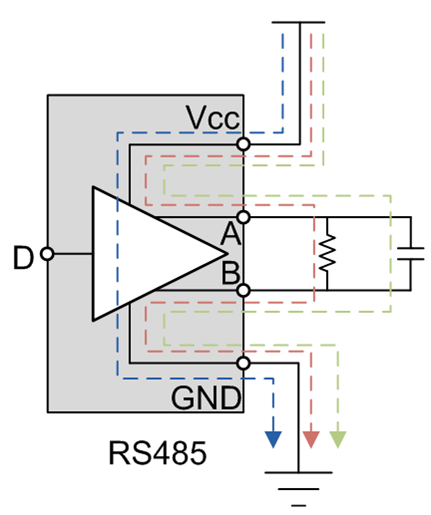

电路设计需要注意:1)MPC2860采用大端(big-end)工作模式,STl6C654从BD0开始接收数据。STl6C654数据总线D[0..7]连接MPC860的数据总线D[7..0],地址总线A[O..4]连接MPVC860地址总线A[31..27];2)STl6C654采用Motorola模式即![]() 接地,此时控制

接地,此时控制![]() 为0,就是对4路串口同时使能,选择A3,A4就可以对具体通道操作;3)采用定时查询模式,STl6C654的

为0,就是对4路串口同时使能,选择A3,A4就可以对具体通道操作;3)采用定时查询模式,STl6C654的![]() 与MPC860的

与MPC860的![]()

![]()

连接,![]() 与MPC860的

与MPC860的![]() 连接,

连接,![]() 置空,以实现了串口数据的接收后以UDP协议包发送到以太网和从以太网收到的UDP包数据按协议重打包后发送到指定端口;4)时钟选择为14.7654MHz,

置空,以实现了串口数据的接收后以UDP协议包发送到以太网和从以太网收到的UDP包数据按协议重打包后发送到指定端口;4)时钟选择为14.7654MHz,![]() 为O,但实际波特率要通过MCRBIT7初始化设置,各路传输速率最高可达921.6 Kb/s。STl6C654电路设计如图3所示。

为O,但实际波特率要通过MCRBIT7初始化设置,各路传输速率最高可达921.6 Kb/s。STl6C654电路设计如图3所示。

评论