ARM7内核的中断屏蔽方法

引言

CPU在执行程序的过程中,由于外部的某种原因,有必要尽快地中止当前程序的执行,而去执行相应的处理程序,待处理结束后再回来继续执行被中止了的原程序,这种情况称为“中断”。从事嵌入式开发的工程师对中断的概念都很熟悉,在x86系列CPU体系中,软件设计人员会调用enable()函数和disable()函数来允许或屏蔽中断。enable()和disable()是两个库函数,函数disable()的作用是屏蔽中断,它唯一允许执行的中断是NMI(不可屏蔽中断);函数enable()的作用与函数disable()相反,是将被屏蔽的中断打开,允许中断。这两个函数的原型都是在头文件DOS.H中定义的,DOS.H定义的都是一些DOS接口函数。DOS的全称为“Disk Operating System”,即“磁盘操作系统”,是一种在x86系列的微型计算机上运行的操作系统。

x86和ARM是两种不同体系的微处理器,ARM不支持DOS接口函数,在ARM公司提供的集成开发环境ADS1.2的头文件中没有DOS.H文件,DO-S.H中定义的所有函数在ARM的编译器中都不支持,所以需要重新设计两个函数替代上述函数,以实现相同的功能。

1 ARM7处理器简介

ARM是Advanced RISC Machines的缩写,ARM公司开发了很多系列的ARM处理器内核,ARM7处理器就是其中的一个系列,其中包括ARM7TD-MI、ARM7TDMI-S、带有高速缓存处理器宏单元的ARM720T和扩充了Jazelle的ARM7EJ-S。该系列处理器提供Thumb 16位压缩指令集和Embeded-ICE软件调试方式,多应用于多媒体和嵌入式设备,包括Internet设备、移动电话、PDA等。

2 ARM7中断工作模式

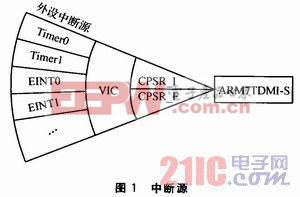

ARM7处理器具有2个中断输入,分别为IRQ中断和FIQ中断,如图1所示。其对应的中断操作模式为向量中断IRQ模式(用于通用中断处理)和快速中断FIQ模式(支持数据传输或通道处理)。

向量中断请求(IRQ)是一个由nIRQ输入端的低电平所产生的正常中断。IRQ的优先级低于FIQ,对于FIQ序列它是被屏蔽的。任何时候在一个特权模式下,都可通过置位当前程序状态寄存器(CPSR)中的I位来禁止IRQ。

快速中断请求(FIQ)支持数据转移或通道处理,在ARM状态中,FIQ模式有8个专用的寄存器可用来满足寄存器保护的需要,这是上下文切换的最小开销。将nFIQ信号拉低可实现外部产生FIQ。在一个特权模式中,可通过置位当前程序状态寄存器(CPSR)中的F标志来禁止FIQ异常。当F标志清零时,ARM7处理器在每条指令结束时检测FIQ同步器输出端的低电平。

3 ARM7中断屏蔽程序实现

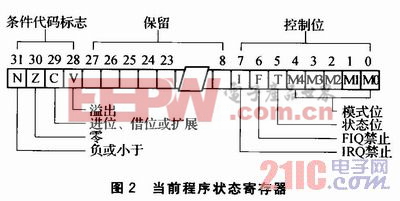

ARM7内核包含1个当前程序状态寄存器(CPSR),该寄存器中包含条件代码标志位、控制中断的使能和禁止位,以及设置处理器操作模式位。当前程序状态寄存器如图2所示。

评论