基于PCIE/104总线的高速数据接口设计

摘要:PC/104作为一种工业嵌入式的总线标准,由于其小尺寸结构、低功耗,以及软件通用性而被广泛用于航空航天、工业控制等领域。这里主要介绍了下一代总线技术PCIE总线在PC/104标准下的应用。阐述了数据接口卡的系统组成和各单元的功能,以及驱动在linux操作系统下的实现原理。自行设计并实现了板卡原理图和PCB,同时简述了高速PCB仿真方面的知识,并针对PCIE差分线进行了版级仿真。最后利用PLX公司提供的开发套件在Linux操作系统下完成了板卡驱动的开发和调试。

关键词:PCIe总线;PC/104;嵌入式;PCB仿真

0 引言

PCIE总线是由Intel公司提出用来取代现行PCI总线的下一代总线技术,被公认为未来总线的发展方向,目前已经成功应用在了商业机上。相对于目前流行的PCI总线,它具有如下特点:

采用了串行点对点模式,数据总线从并行走回向串行无疑是一个趋势,如现在流行的SATA总线、PCIE总线和rapidIO总线都是串行总线。现在串行总线在速度上的优势可以说是毋庸置疑的。PCIE总线在每个方向上都有X1,X2,X4,X8,X16或X32个信号对,用户可根据不同的需求采用不同的配置。同时串行信号还具有管教更少,便于调试的优点。

PCIE采用了基于数据包的协议来编码事物,而不是PCI体系结构的总线周期。数据包被串行发送和接受,并被字节拆分来通过物理链路。链路上实现的通道越多,数据包发送的数据越快,链路的带宽也越宽。同时PCIE还定义了各种类型的数据包,如存储器读/写请求、I/O读/写请求、配置读/写请求、消息请求和完成数据包等。

PC/104标准是一种嵌入式的总线标准,具有功耗低,尺寸小,堆栈式结构的特点。随着目前各种应用数据传输量的增大,现行的PCI总线在带宽方面已经略显疲态,而新近瑞士逻辑提出的PC/104 Express标准,使得PCIE总线技术被成功地应用在了PC/104标准的板卡上。本文采用了PLX公司的PEX8311桥接芯片,完成了PCIE到局部总线接口的转换,应用PLX公司提供的开发工具在Linux操作系统下实现了板卡的驱动应用。在软硬件两方面进行了设计,完成了PCIE/104板卡的功能,升级了系统的总线。

1 PCIE/104高速信号接口卡的系统

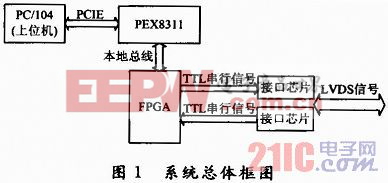

PCIE/104高速信号接口卡的系统设计方案如图1所示。

外部传感器采集到的数据通过LVDS,RS 422等电平方式,以固定的不同串口波特率传到FPGA内部集成的各自对应的双口RAM中。当写入了固定字节后,设定标志位stage为1,同时发出中断信号LINT#给PEX8311。PEX8311产生了assert_INT1信息,并通过PCIE接口发给上位机。上位机保存好现在的任务后,通过PCIE开始发出存储器读命令给PEX8311。PEX8311获得命令后,向FPGA发出本地总线申请信号,FPGA作为本地端的控制器将本地总线控制权交给PEX8311。PEX8311开始读数据,首先要进行的是读取标志位,在读取了标志位后,上位机就知道是哪几路串口信号需要读入。然后,把标志位清掉,这样相当于清掉了中断信号。接着,中断服务程序在进入到各个串口的RAM中,来读取相应的数据。在多路串口信号传输过来时,针对该系统,采用的是优先满足高速串口的原则,也就是采用高速串口的标志位作为中断信号,每次产生中断后查询其他标志位。数据到上位机后待处理。该系统目前实现的是两路串口,而多路串口原理相同。

评论