总线实现片内硬件调试支持单元设计

片上系统的出现使得芯片可以实现更加复杂的功能,获取更高的性能,但同时其内部信号也变得越来越难以观察和控制,相应的测试和调试工作也遇到了难以克服的时间复杂性困难。国际半导体技术路线图( Internat io nal Technolo gy Roadmap for Semico nducto rs,IT RS) 指出,调试和定位问题所需要的时间将会随着工艺的进步呈指数型增长。由于测试和调试工作的复杂性,其费用往往比设计费用还要高,大约要占整个SoC 总设计成本的1/ 3 以上。在整个SoC 的硬件设计过程中,从第一次投片到最后成功的实现所有功能,硬件调试的时间已经接近整个时间的35%,而且这个数字随着集成度的提高还会增加。

本文引用地址:https://www.eepw.com.cn/article/150345.htm 在整个片上系统中,微处理器是核心,也是最复杂的模块,所以各个处理器内核的提供商也都投入了大量的研发力量,在其内核中集成了丰富的调试功能。当今流行的调试技术大多采用复用JT AG 的调试方案,但是这种方法一般都是在目标系统内部插入扫描链,当处理器高速工作的时候,难免会限制处理器性能的提高。

为此,该设计提出一种新的调试结构,它不依赖JTA G接口且需要较少的引脚开销,通过挂接在片上高速总线上来实时监测片内通信状况,同时它直接与处理器进行交互,能够在不影响处理器正常工作的情况下控制处理器以及访问所有片上存储单元,用户可以通过专用的数据输出链路进行远程调试,发布调试指令以及获取反馈信息。结合以上特点,该设计将以文献[ 3]中提出的一个良好调试结构所需具备的三个基本特征作为设计出发点: 调试的可观察性; 调试的可控制性; 高效的通信效率; 低入侵性。

1 调试系统构成

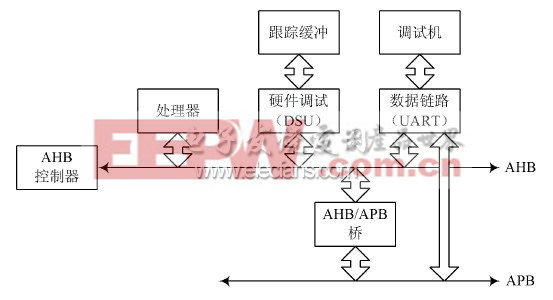

以硬件调试模块DSU 为核心,AMBA 2. 0 总线为构架,专用UART 为调试链路接口的系统结构如图1所示。

图1 调试系统结构图

调试主机通过总线接口U ART 对调试单元发出调试指令; 调试单元将控制系统的调试状态,在满足触发条件时将通过与处理器的直接通信来挂起处理器,用户可以利用调试主机通过调试接口访问片上所有存储单元,获取系统状态信息; 总线追踪缓存可以工作在两种模式下,在正常模式下通过DSU 实时记录总线通信状态,而在调试模式下,将由调试主机对其进行访问,寻找问题发生的根源; 指令追踪缓存处于微处理器内部,用来存储执行过的指令; 调试接口UART 将为调试主机和总线之间提供协议转换服务,实现串行数据与并行数据的相互转化。

1. 1 AHB 总线

在SoC 设计中,芯片内部总线的设计往往决定了芯片的性能、功耗与各模块的复杂度。通常依据以下两个方面选取总线: 一是芯片设计流程其内在的需求,二是对交换带宽、延时和效率灵活性的需求。该设计采用ARM 公司提出的一种片内高速总线协议AHB,它具有以下特点: 支持突发传输; 支持分块传输; 单周期总线控制权移交; 单时钟沿操作; 非三态执行; 宽数据总线架构; 数据和地址流水重叠。此外,该协议还支持静态时序分析以及友好的测试插入。

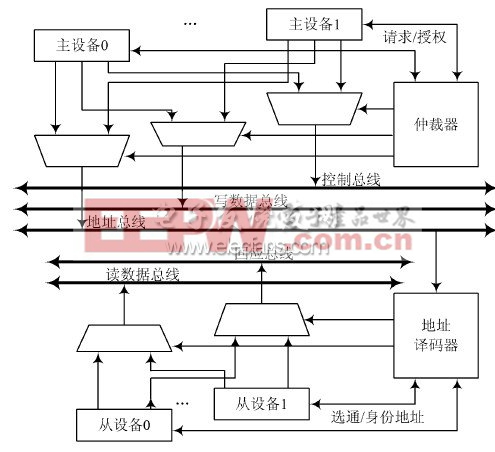

该系统设计的AHB 结构如图2 所示,由主从模块、仲裁器以及地址译码器构成,采用中央多路选择器的互联方式。作为核心部件,仲裁器接收最多16 个主设备的总线请求,为实现 可配置!的设计初衷,采用基于分治的仲裁策略,实现了固定与轮询两种优先级算法,可以供用户灵活选用。AHB 采用的集中式地址译码机制,有利于提高外围设备的可移植性,中央译码器根据地址总线发来的地址以及各个从机的身份信息进行译码以选择从设备,该设计为减少运算逻辑和降低功耗,仅对地址的高端位进行判别。整个AHB 系统由多路选择器连接起来,避免了采用三态总线带来的功耗、速度以及可测性方面的问题,系统所需的控制信号和地址数据将由多路选择器路由到相应的目的设备,而根据路由的方向可将多路选择器分为主模块到从模块多路选择器和从模块到主模块的多路选择器。此外,为了解决在没有主机请求总线时的总线停靠( bus parking ) 问题,此系统还设计了一个缺省主设备( default master) ,其选择停靠的主机号依赖选取的仲裁算法。split 传送是AHB 的一个显着特点,它在防止系统死锁和充分利用总线方面起到了积极作用,这里为了解决分块锁定( split lo cked) 这一矛盾以及地址未命中问题,设计实现了一个虚拟从设备( dummy slave) ,当以上问题出现时,将由虚拟从设备代为发送回应信号。

图2 AH B 总线系统互联结构

1. 2 T race Buf fer

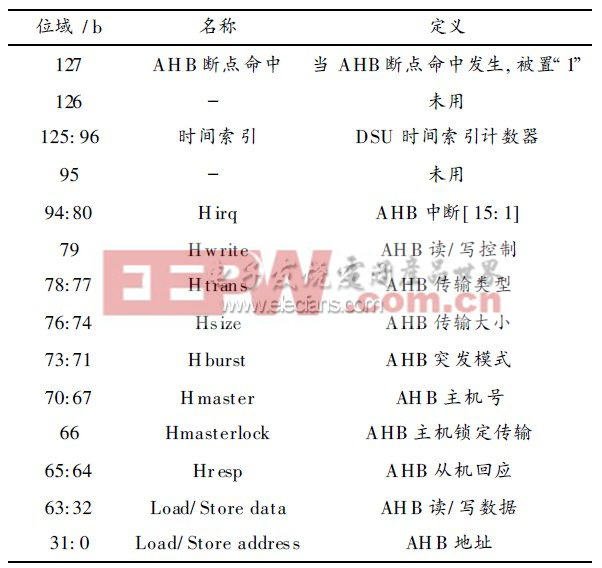

为了实现引言中提到的调试的可观察性,本系统中就必须具备能够记录总线通信信息以及指令执行情况的模块。AHB T race Buf fer 就是一个循环缓冲存储体,被用来存储AHB 上通信的所有信息。AHB 总线上的地址、数据和各种控制信号存储在其中,并且可以在以后的分析中读出; 同时在需要调试写入的时候也可以通过AHB 写总线写入数据。本模块因每个周期需记录的信息位宽为128 b,所以设计的AHB TraceBuf fer 存储器将采用4 个位宽为32 b 的同步SRAM构成,深度可配置。若整个Buffer 的容量为1 KB,则每一个SRAM 大小为64 × 32 b,若容量为2 KB,则每一个SRAM 大小为128 × 32 b,依次类推。

在正常总线通信中,每一笔AHB 传输将被循环存储到Buffer 中,在处理器进入调试模式后,AHB TraceBuf fer 被暂时挂起,这时可由外部调试设备利用AHB总线访问Buffer ,通过地址译码控制4 块SRAM 各自的使能信号,进而完成读/ 写操作。Buffer 的数据输入端为128 b,包含的有地址、数据、控制信号和控制寄存器值等,详细见表1。

同样在微处理器内部实现一个指令T race Buf fer,用来存储执行过的指令。该部件同样循环存储,位宽128 b,利用4 块SRAM 构成。该存储器中将记录指令执行过程中指令运行状态,操作码、操作数和操作结果,以及PC 指针等值,用以方便以后读出进行诊断定位。

两块Buf fer 在系统正常运转时记录数据,所以为了保证其内容的正确性,仅允许系统进入调试模式时对其进行读写访问,而正常状态下将禁止对其访问。

表1 AHB Trace Buffer 数据分配表

1. 3 DSU 单元

对于嵌入式系统而言,其内部的大部分信号与微处理器的工作状态对于开发者都是不可见的,本设计就是通过提高在系统开发过程中用户对系统的可观察性和可控制性从而帮助开发者更为有效的定位设计中的错误,从而加速开发周期。为此,本系统必须在片上集成单独的调试单元用于监测系统运转并能接管处于异常状态时的微处理器。

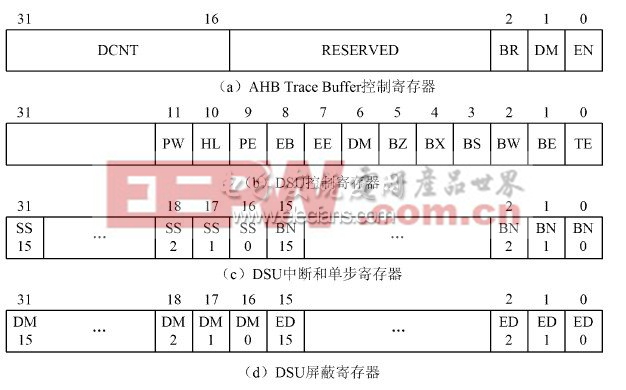

借鉴CPU中程序状态字的作用,DSU 中首先需要一些寄存器能够控制与管理整个调试单元的行为,它应该能接收来自调试主机发布的调试命令,同时也能够对系统内部断点等触发行为做出实时响应以及在任何时刻都能被调试主机所访问,为此,该调试单元设计了如图3 所示的部分关键寄存器。

图3 DSU 内部寄存器

图3( a) 为AHB T race Buf fer 控制寄存器。其中EN 位将控制AHB Trace Buffer 的使能; DM 位表示Buf fer 处于延迟计数模式,设计这种模式是为了方便观察断点发生前后定长时间内系统的运转状态; BR 位则表示AHB 断点命中; 高16 位DCNT 表示在延迟计数模式下的延迟计数值。AHB 断点寄存器有两路,可写入30 位的精确断点地址,当AHB 地址总线上广播的地址与该断点地址相吻合时,将会立即冻结AHBTr ace Buf fer,同时清除AHB 控制寄存器的使能位。

评论