嵌入式系统芯片的软硬件协同仿真环境设计

摘要:针对嵌入式系统芯片SoC开发验证阶段的需求,介绍了一种通用的SoC软硬件协同仿真平台。软件仿真由C/C++和汇编语言编写,硬件仿真基于VMM验证方法学所搭建,SoC设计代码由RTL代码编写而成。将SoC设计代码中的ARM由DSM模型替代,通过VCS编译器将软硬件协同起来进行信息交互,实现一种速度快、真实性高、调试方便的通用性仿真平台。

关键词:协同仿真;DSM模型;验证方法学;片上系统

1 概述

随着微电子产业日新月异的发展,IC设计的规模越来越大,集成度越来越高,已经足以将一套完整的系统集成到一块小小的芯片中。在这种形势下,SoC技术应运而生。随着IP核复用技术的出现,SoC芯片的设计已经不再是很大的难题,SoC芯片的验证已逐渐取代芯片设计成为芯片开发阶段的瓶颈。现阶段SoC芯片设计的正确性要经过前仿真、后仿真以及FPGA验证来保证。前仿真包括单元验证、集成验证和系统验证,后仿真包括带反标时序SDF的网表仿真,其中系统验证和后仿真都需要关注SoC芯片的全局功能,这就涉及SoC的软件仿真和硬件仿真的协同问题。本文以DSM模型替代ARM核,以VMM验证方法学和VCS仿真器为基础,搭建一个可重用性高、调试和定位问题方便、仿真真实性高、软件和硬件能够很好配合的协同验证平台。

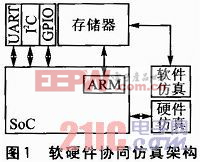

软硬件协同仿真架构如图1所示,协同验证分软件验证环境和硬件验证环境两部分。软件代码通常由C/C++和汇编语言混合编写而成,然后由软件编译器转换成二进制格式,最后将该二进制文件加载到SoC芯片的存储器中去,芯片boot启动时由ARM核调用软件代码并执行;硬件环境基于VMM验证方法学进行搭建,下文中会有详细介绍。协同仿真就是通过事件和命令,使用一些机制,在这两个环境间进行控制。

2 DSM模型的使用

SoC芯片的CPU一般选用ARM,协同验证平台中ARM可以用seamless CVE模型替代,或者直接选用ARM网表。采用seamless CVE模型进行仿真,虽然速度比较快,但需要替换设计中的Memory模型,且必须使用CVE自己的模型,这样与芯片真实情况有出入;采用ARM网表进行仿真,速度比较慢,调试也不方便,但是更接近实际情况。相比于这两者,本文采用的DSM(Design Simulation Model)模型由ARM公司提供,能完全模拟ARM的接口和时序行为,具有更高的真实性,而且DSM无需更换存储器模型和外挂仿真工具,使验证DUT与实际芯片完全一致,即不必为了满足仿真需求修改部分RTL代码。此外,DSM环境仿真过程中输出的LOG文件log.eis真实记录每个周期执行的CPU代码和操作。根据该文件能快速定位软件问题。CVE环境通过调用XRAY软件调试工具,虽然可以进行单步调试、没置断点等操作,但出现软件问题时定位没有DSM环境那么直观、方便。

评论