嵌入式系统芯片的软硬件协同仿真环境设计

验证的总体架构是分层次的,层次化的验证环境具有很好的扩展性和重用性,各个层次完成自己特定的功能。Test层又叫TC层,主要完成数据激励的定义、环境的控制工作。Generator层定义的数据“模板”,产生各种数据激励。Function Layer层完成输入和输出数据激励的收集,进行自动比对。Command Layer层主要按接口时序收发数据,同时将一些底层方法(如数据读写等)进行封装。Signal Layer层主要是完成接口信号连接工作。不同的人关注不同层次,一般的验证人员只需要在Test层工作,编写测试向量。只有搭建环境的验证人员才需了解各个层次。验证架构的层次化降低了验证环境复杂度和环境维护成本,提升了验证效率。本文引用地址:http://www.eepw.com.cn/article/150062.htm

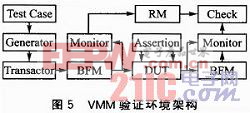

本文基本采用图4的验证环境架构的思路,并在其基础上进行修改,添加相应组件。VMM验证环境架构如图5所示,环境数据流从测试用例Test Case开始,经过数据包产生器Generator和数据处理器Transactor送给BFM处理,BFM把验证环境的抽象层次从信号级抽象到Transaction级,在实现上只做时序转换功能,利于重用。从发送方向看,BFM只负责将接收到的数据发送给DUT;从接收方向看,BFM只负责将接收到的数据发给Transactor,实现任何数据的解析。Monitor抓取接口上的信号,并分析各组控制信号之间的逻辑时序关系,检查其是否满足协议所规定的逻辑时序关系,同时把监测到的数据信号转化为数组送到RM解析。与BFM一样,Monitor只实现时序转换功能,不做数据解析。从Monitor上采样数据再送入RM,是基于重用的角度考虑。参考模型(RM)用于预测数据响应,Check组件将RM的输出数据与被观测响应进行比较。

该验证环境架构还添加断言(Assertion)来提高观察和定位设计问题的能力。断言是检查DUT中信号行为是否正确的观察器,用来描述被预期的特定性质。本文采用的断言为SVA断言语言,可以应用到设计过程的各个阶段,还可以统计功能覆盖率。

5 基于DSM的软硬件协同仿真调试

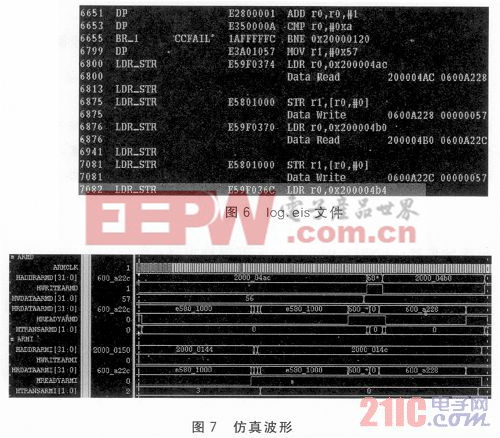

由于DSM模型在仿真过程中,会将ARM执行的每一步动作打印出来,生成一个log.eis文件,由该文件给出的信息定位问题非常方便,如图6所示。

图中第1列表示程序执行到ARM的第几个时钟周期。第2列是ARM执行的指令类型。第3列的CCFAIL表示条件执行时是否执行,如果条件执行了,则不打印CCFAIL,反之则打印出CCFAIL。第4列是ARM执行的机器码。最后几列是详细的ARM执行的动作,从图中可以看出ARM执行哪一步指令,将哪些数据读写到哪些地址。对应的仿真波形图如图7所示。可以看出,log.eis完整无误地将ARM执行的动作打印了出来。

结语

设计验证是SoC设计的关键技术之一,贯穿整个SoC设计过程。随着SoC技术的发展,软硬件协同验证的效率和正确性对整个SoC设计的影响也越来越大。相比传统的软硬件协同环境,本文介绍的环境速度快,更真实,调试也更加容易。该环境可继承性好,能够为各种SOC项目开发验证所用。

评论