嵌入式系统中存储器性能研究

摘要:动态随机存储器是嵌入式系统的一个重要组成部分,而动态随机存储器故障是嵌入式系统故障的一个主要原因之一。在此从动态随机存储器的结构和失效模型出发,有针对地提出了用于检测性能的数据和读写方式,实验证明通过提出的检测方法能够有效地找出潜在的存储器故障,从而能够为嵌入式系统设计人员提供改善系统性能的方法和途径。

关键词:嵌入式系统;动态随机存储器;故障检测;失效模型

0 引言

随着超大规模集成电路的制造工艺的进步,在单一芯片上动态随机存储器实现了更高密度的比特位,使得计算机系统在计算速度迅猛发展的同时,内存容量极大的扩大。伴随着集成度的提高,存储器单元呈现失效的可能性随之增大,失效的形式和原因也趋于更加复杂化。存储器测试的目的是确保其每个单元能够存储数据并且惟一的寻址、读、写。存储器的测试面临两方面的要求:较高失效类型覆盖率,尽可能检测出潜在的存储器故障;较少的存储器操作,以便缩短检测时间。因此存储器测试应能够在一定的测试时间内得到可能的最佳故障覆盖率。由于对存储器进行物理检测是不可能的,可行的办法是将待测存储器的访存结果与认定无故障的存储器的访存结果做比较。

1 DRAM的原理及失效模型

动态内存的结构和ROM及SRAM有较大的不同。图1是动态内存的总体结构。内存单元按照行、列组成阵列。地址首先分为行地址和列地址,行地址经过译码器,选中一行内存单元。列地址选择数据输出到数据输出端。

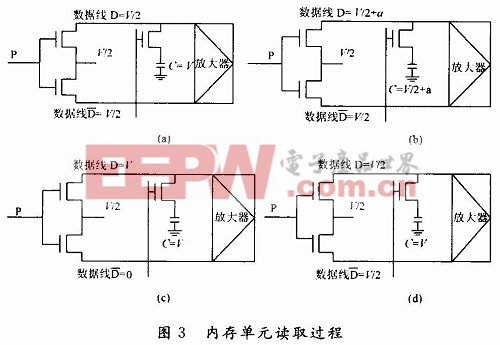

电压均为0.5 V,T1,T2,T3均截止。首先,T3导通,电容上的电荷使数据线D上电压为0.5 V+a。放大器对信号放大,使得数据线D上电压为V,上电压为0,读出数据“1”(图3(b)),同时对电容充电,电容电压为V(图3(c))。然后T3截止,T1,T2导通,数据线D,上电压恢复为0.5V。电路恢复初始状态(图3(d))。

假设存储器实效仅仅被单元状态的跳变所激活,即不考虑不改变状态的写操作时出现的失效。存储器的失效模型可以表述为如下:

(1)粘滞实效(Stuck-at Faults,SF)。一个或多个存储器单元固定为s,s∈(0,1),不因对该单元的读写而发生状态的变化。

(2)组合实效(Coupling Faults,CF)。存储器某些位的跳变导致其他位的逻辑值发生非预期的变化。组合失效的产生归咎于单元物理上毗邻所产生的分布电容或者是单元间的电流泄漏。2个存储单元之间的组合失效称双组合实效。例如:对于单元j的一个0→1或是1→0的写操作将会改变i单元的内容,使之状态翻转。但是反之i单元的状态改变并不一定也会对j产生影响。

(3)地址译码故障(Address Decoder Faults,AF)。有4种情况:某地址不能访问任何单元;某单元无法被任何地址访问;某地址可以同时访问多个单元;某单元可被多个地址访问到。

评论