解析嵌入式系统串扰问题

引言

本文引用地址:https://www.eepw.com.cn/article/149460.htm在嵌入式系统硬件设计中,串扰是硬件工程师必须面对的问题。特别是在高速数字电路中,由于信号沿时间短、布线密度大、信号完整性差,串扰的问题也就更为突出。设计者必须了解串扰产生的原理,并且在设计时应用恰当的方法,使串扰产生的负面影响降到最小。

1 串扰理论分析

串扰主要源自两个相邻导体之间所形成的互感与互容。在高速数字电路中,互感通常比互容的问题更严重。

1.1 互容

一个电路产生电场,该电场会影响第二个电路,这种相互影响的系数称为它们的互容。

式中,CM为互容,ΔV为驱动波形的阶跃幅度,TR是驱动波形的上升时间,RB是接收电路的接地阻抗。

由式1可知,互容串扰电压与CM、ΔV/TR 、成正比,因此,减小互容串扰电压的方法有:

② 减小ΔV/TR。在确保信号时序的前提下,尽可能选择信号沿较缓的器件。

③ 减小RB。减小被干扰电路接地阻抗,对被干扰电路进行末端端接,为被干扰电路并接去耦电容。

1.2 互感

两个信号回路相互靠近时,一个信号回路的磁场变化将影响另一个信号回路,这种影响就是互感。互感的大小取决于信号回路的自感与两个信号回路耦合的程度。

式中,LM为互感,ΔV为驱动波形的阶跃幅度,TR是驱动波形的上升时间,RA是驱动电路的源端阻抗。

由式(2)可知,互感串扰电压与LM、ΔV/TR 成正比,与RA成反比。因此,减小互感串扰电压有如下方法。

(1) 减小LM

① 增大信号走线间距(因为LM随着间距平方的增加而下降,关键信号可采用3W原则)。

② 为信号提供完整的参考平面。在低速电路中,电流沿着电阻最小路径前进,而高速信号沿着电感最小路径前进。电感最小的返回路径就紧贴在一个信号导体下面,它使输出电流路径与返回电流路径之间的总回路面积最小,从而使输出电流路径与返回电流路径的干扰磁场相互抵消。

③ 减小信号到参考平面的距离,从而减小环路面积,达到减小LM的目的。

④ 尽可能地减小相邻信号间的平行长度。平行长度越短,则总的LM越小。

⑤ 无参考平面隔离的相邻信号层走线方向应该垂直,可减小磁场耦合程度。

⑥ 对串扰较敏感的信号线尽量布在内层,以减小磁场耦合程度。

(2) 减小ΔV/TR

在确保信号时序的前提下,尽可能选择信号沿较缓的器件。

(3) 增大RA

在干扰电路源端串接电阻,减小电流变化斜率,同时要兼顾与传输线阻抗匹配,避免信号反射。

1.3 近端串扰和远端串扰

图1 两条传输线的耦合

如图1所示,假设位于A点的驱动器是干扰源,而位于D点的接受器为被干扰对象,那么驱动器A所在的传输线被称为“干扰源网络”或“侵害网络(Agreessor)”,相应的接收器D所在的传输线网络被称为“静态网络”或“受害网络”。静态网络靠近干扰源一端的串扰称为“近端串扰”(也称后向串扰),而远离干扰源一端的串扰称为“远端串扰”(也称前向串扰)。根据产生的原因不同,可将串扰分为容性耦合串扰和感性耦合串扰两类。

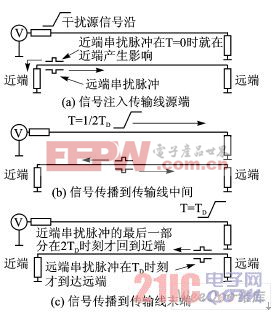

受侵害线上近端和远端串扰噪声的波形可以通过图2得出。当一个数字脉冲上升沿进入传输线,它将不断地在受侵害线上感应出噪声,一部分串扰噪声将传向近端,另一部分将传向远端。远端串扰脉冲与侵害线上的信号经过时间TD(信号在传输线上的延迟时间)后同步到达终端。近端串扰脉冲将起始于侵害线上信号变化沿出现的时刻,而侵害信号到达终端前产生的最后一部分近端串扰信号将在t=2TD时刻才到达近端,这是因为这部分信号要经过整条传输线才能被传回近端。所以,近端串扰起始于t=0,并且持续2TD的时间。远端串扰起始于t=TD,持续时间为数字信号的上升或者下降时间。

图2 串扰噪声示意图

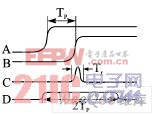

近端和远端传播的容性耦合电流都是正向的。具体的容性耦合如图3所示,图中的TP是干扰信号在传输线上的延迟时间,Tr是干扰信号的上升时间。

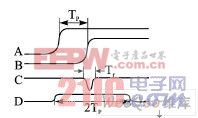

流向近端的感性耦合电流与近端容性耦合电流同向,流向远端的感性耦合电流与远端容性耦合电流反向。具体的感性耦合如图4所示。

图3 容性耦合的近端、远端串扰波形

评论