可扩展式处理平台提升嵌入式系统性能

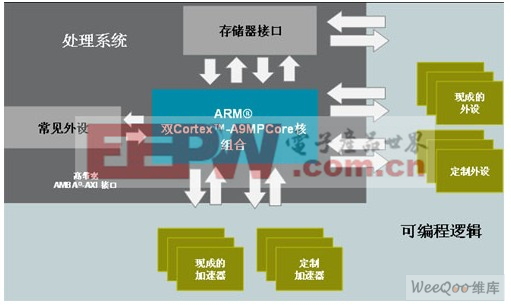

无论是汽车驾驶辅助、智能视频监控、工业自动化、航天与国防或是无线通信等终端应用,功能的日益复杂使得嵌入式系统对性能、功耗、成本、尺寸和灵活性提出了更高要求。为此,赛灵思公司(Xilinx)推出全新的可扩展处理平台(Extensible Processing Platform)架构,该平台将完整的ARM Cortex-A9 MPCore处理器片上系统(SoC)与集成了28nm低功耗和高性能的可编程逻辑结合在一起,使得嵌入式系统设计人员可同时拥有串行和并行处理能力,减少开发应用基础设施所花费的时间,最终实现产品差异化设计。

本文引用地址:https://www.eepw.com.cn/article/148760.htm与以往以FPGA为中心的开发方式不同,赛灵思可扩展式处理平台为嵌入式系统设计人员提供了一种以ARM处理器为核心的设计和开发方法,以实现强大的计算与处理能力,同时降低成本与功耗。开发人员同时采用串行(使用 ARM 处理器)和并行处理(使用可编程逻辑)功能,以满足应用对较高性能的需求,同时更高集成度还能带来低成本、低功耗和小型化等优势。

此外,通过高带宽AMBA-AXI互联与处理器系统紧密结合,可编程逻辑能够使用现成的IP和/或定制IP将关键的系统功能速度提升高达100倍。这种架构方法不仅能解决并行和串行计算环境、存储器以及I/O之间的常见性能瓶颈问题,而且还能让处理器系统实现包括动态重配置在内的可编程逻辑配置控制。

ARM中国总经理兼销售副总裁吴雄昂表示,ARM多核应用处理器对第三方软件有广泛的支持,如Flash等,它具有非常强大的处理能力而且功耗更低。另一方面,接口的处理能力在很大程度上决定了整个系统的性能,采用不同的接口,系统运算能力将会产生很大区别。“我很高兴看到,在新的AMBA/AXI接口上,能够获得很好的数据吞吐能力。”吴雄昂说。

赛灵思最新的28nm高性能低功耗工艺广泛应用在该架构上。赛灵思公司全球市场营销及业务开发高级副总裁Vin Ratford介绍:“统一的FPGA架构提供了可扩展性的产品系列,并使整体功耗得到大幅降低,其中静态功耗可以降低50%。”硬件和软件共同开发的流程使系统架构师和软件开发人员能够在他们熟悉的编程环境中并行开展工作,他们不仅能就系统功能与性能尽早做出决策,而且还可在整个开发过程中轻松进行修改。

这种以软件为核心的开发流程能够提供完整的处理器系统,包括高速缓存、存储控制器以及常用的连接和IO外设,并能在开机时启动并运行目前流行的各种操作系统,如Linux、风河系统的VxWorks、Micrium的uC-OSII等。“当复位启动的时候,硬核SoC将会自动启动操作系统,而不会等到FPGA先启动。”Vin Ratford强调。ARM架构及ARM Connected Community行业生态系统则进一步帮助嵌入式系统开发人员提高生产力,同时通过在ARM每个内核速度高达800MHz的双核Cortex-A9MPCoreA9 MPCore处理器构建赛灵思的子系统架构,并结合赛灵思高性能、低功耗28nm可编程逻辑的并行处理能力,可以实现卓越的高性能。

Vin Ratford指出,“软件与硬件共同开发的一个重要优势就是硬件工程师在开始系统架构的同时,软件工程师也可以开展他们设计,这时候,工程师可以比较硬件和软件环境,找到系统的瓶颈,还可以实现硬件加速。与传统设计流程不同的是,赛灵思新的可扩展平台是以软件工程师为主导,从开发第一天开始软件工程师就可以开始做设计,因此效率大为提升。”

软件开发人员可以充分利用基于ARM技术的现有系统代码,并使用大量现成的开放源代码以及已经商用的软件组件库。“我们支持一些主流的操作系统,如Linux等,其IP核可由ARM强大的生态系统提供,使赛灵思的工具得到充分发挥。这将有助于客户的产品更快进入市场。”Vin Ratford说。

赛灵思可扩展式处理平台。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论