基于ARM的用户可定制SoC

面对当今竞争激励的市场,嵌入式系统设计人员不得不重新审视其设计和开发过程。系统越来越复杂,性能、功耗和空间限制也越来越大,传统的方法已经达到了极限。同时,不断变化的标准、新出现的市场和发展趋势都要求设计过程非常灵活,能够积极应对这些变化。设计人员不仅需要开发更复杂的系统,而且还要能够迅速实现新的或者衍生设计。

设计团队有如此多的需求,因此,增加开发时间和资源以适应这些需求是合乎逻辑的,但实际上相反。越来越窄的市场窗口要求他们在更短的时间里推出更高级、更灵活的系统。更麻烦的是,经济因素的限制也迫使很多设计团队缩减规模,而不是增加人员。他们今后要获得成功,关键是采用更高效的手段来迅速实现功能丰富的高性能自适应产品。

出现了新的解决方案

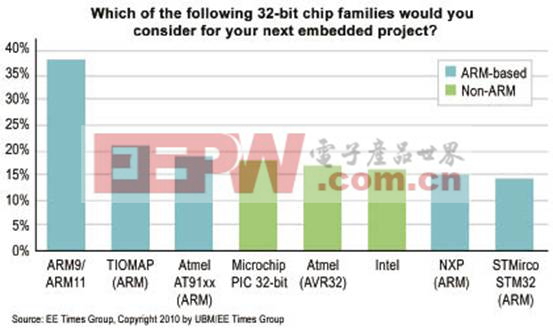

在市场开发中有利于设计人员的一面是嵌入式系统的主要平台采用了ARM处理器。仅仅几年前,处理器市场还是四分五裂,PowerPC、RISC、MIPS和SPARC都在竞争实现更广泛的应用。市场现在已经非常成熟,在嵌入式应用中,很多用户采用了ARM处理器作为实际的标准(图1)。结果,越来越多的出现了基于ARM的解决方案,从标准产品到软核ARM IP,直至在可编程逻辑和ASIC中实现的硬核IP等。

图1

即使如此,通用嵌入式系统也很难满足现代设计需求。多芯片解决方案实现起来相对容易一些,但是成本高,缺乏设计人员所要求的灵活性以及性能/功耗指标。采用了软核处理器的单芯片解决方案实现起来也相对容易一些,但是性能有限。另一方面,ASIC SoC具有板上增强ARM内核,功耗和性能表现非常出色,但是对于大部分应用而言,由于开发时间长、不灵活,以及成本太高等问题,因此面市时间较长。

为提高竞争力,嵌入式系统开发人员需要一种能够帮助他们开发独具优势产品的解决方案,非常灵活,效率也非常高。

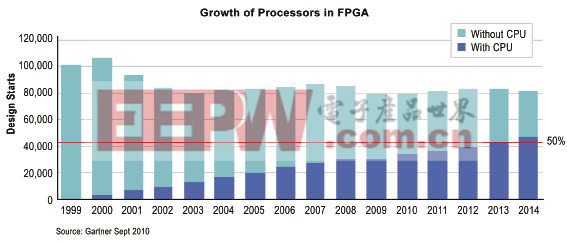

基于FPGA的单芯片实现方法具有低成本和快速面市等优点,是多芯片和ASIC SoC非常有吸引力的替代方案。实际上,在过去十年中,FPGA内置嵌入式处理器的应用在稳步增长(图2)。但是,并不是所有基于FPGA的解决方案都能够满足目前苛刻的需求。传统上,使用基于HDL的“软核”ARM来实现基于FPGA的ARM系统。对于密度、功耗或者性能要求不高的系统,这一方法是可行的,但是不一定能满足更复杂系统的要求。对于不断发展的系统,在FPGA平台上结合经过优化的硬核ARM是很好的解决方案。

图2

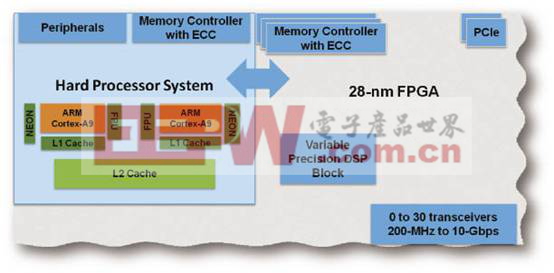

由于FPGA供应商在技术上的进步,市场上出现了新一类SoC器件,满足了目前嵌入式系统应用的多种功能需求。基于ARM的SoC FPGA在一个SoC中结合了增强ARM处理器、存储器控制器以及外设和可定制FPGA架构。

基于ARM的SoC FPGA (如图3所示)在单片FPGA中紧密结合了经过优化的“硬核”处理器系统(HPS)模块。HPS包括双核ARM处理器、多端口存储器控制器以及多个外设单元,处理器性能达到4,000 DMIPS (Dhrystones 2.1基准测试),功耗不到1.8 W。这些硬核IP模块提高了性能同时降低了功耗和成本,减少了对逻辑资源的占用,突出了产品优势。设计人员可以定制片内FPGA架构,开发专用逻辑。可编程功能支持灵活的通信标准和网络协议。

图3

评论