FatFS的水动力实验数据存储系统设计

摘要:针对在水动力实验研究中数据量集中、数量多的问题,提出了一种基于FatFS文件系统的SD卡存储系统设计方案。该系统以ST公司的STM32F103ZET6为核心,通过SDIO接口实现大量数据文件存储。详细讲解了系统的USB模块、RTC模块等硬件设计,探讨了在系统上移植FatFS文件系统的要点,并在SD卡上实现了FAT文件的读写功能。该系统传输速度快、可靠性强,具有一定的应用价值。

关键词:STM32F103ZET6;数据存储;SD卡;FatFS

引言

在水动力的实验中,通过改变模型外形设计、迎水角度、水流速度等参数观察空化现象对模型的影响。参数变化对应记录一组实验数据,而整个实验过程,共有几十组实验数据需要分别采集、记录。同时,实验中空化产生到溃灭过程最好都能记录下来以供后续研究。因此,对实验中采用的数据采集系统提出了数据短时集中、文件数量多的要求。

本文采用了以SD卡为存储体,采用FAT文件系统记录数据的架构来处理数据。SD卡的核心是NANDFlash,由于体积小、功耗低的优点被广泛应用于各类电子产品中。采用文件系统能够对大容量存储媒介进行高效的管理,并且适合于主流的Windows操作系统。文件系统采用开源的FatFS,实现了使用FAT文件系统的数据存储系统。FatFS是专门为嵌入式系统设计的FAT文件系统模块,它是免费开源的,完全用标准C语言编写,具有良好的硬件平台独立性,可以移植到多种嵌入式处理器上。

1 系统结构

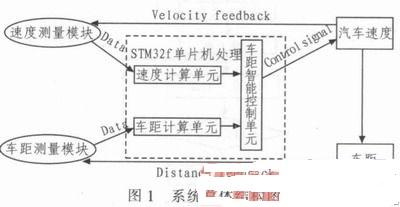

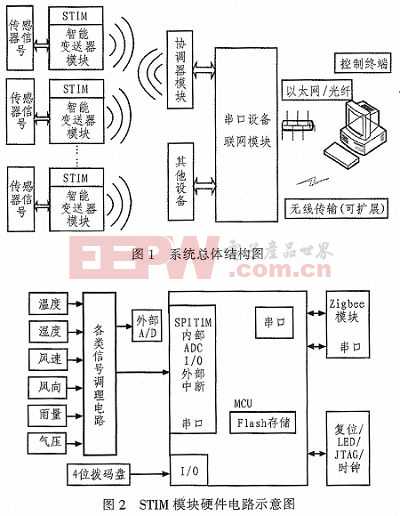

数据存储系统结构如图1所示。该数据存储系统以ST公司的STM32F103ZET6为核心控制芯片,与上位机通过串行通信接口发送数据,或者USB接口直接写数据,控制芯片以FAT文件的形式存储在SD卡中。其自带的RTC单元将存储的数据文件以实时的系统时间命名,并在文件内容中也加入时间戳等信息,方便多个文件后期处理。由于实现了文件系统,用户利用USB接口时,该系统被识别为U盘,可以用PC机进行任意的文件读写操作。

2 硬件结构

2.1 微控制器

STM32是ST公司推出的基于Cortex—M3内核的32位ARM芯片系列,本系统选用了STM32F103ZET6作为主控MCU,这个芯片属于STM32F103系列的高容量芯片,片内Flash容量为512 KB,片内SRAM容量为64KB,LQFP144封装,72 MHz主频。具备完整的FSMC总线,26位地址线和16位数据宽度,即支持各种类型的SD卡接口。

2.2 MicroSD模块

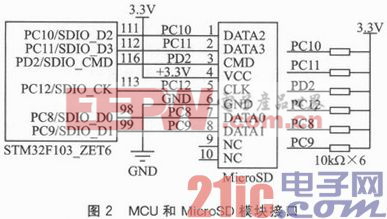

STM32F103ZET6微控制器的SDIO单元在AHB外设总线和SD卡设备问提供了操作接口,支持不同的数据总线模式。SD规范协议中定义了对SD卡的两种访问模式:SD模式和SPI模式。SD模式允许4线的高速数据传输。SPI模式允许简单地通过SPI接口来和SD卡通信,这种模式同SD模式相比丧失了速度优势。在本系统中,采用了SDIO接口来访问SD卡,即SD模式。STM32F103ZET6和MicroSD模块接口如图2所示。

2.3 USB接口硬件

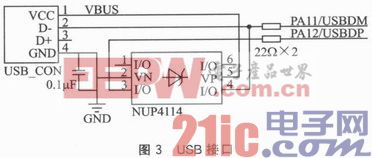

STM32F103ZET6的USB单元实现了USB2.0全速总线和APB1总线间的接口,增强了系统的兼容性。还采用USB接口ESD防护器件NUP4114,满足ESD防护标准IEC61000-4-2(ESD15kV air,8 kV Contact)。其USB外设支持USB挂起/回复操作,可以停止设备时钟实现低功耗。USB接口如图3所示。

2.4 RTC模块

STM32F103ZET6的实时时钟RTC模块是一个独立的定时器。RTC模块拥有一组连续计数的计数器,在软件配置下,可提供时钟日历的功能。RTC硬件都集成在处理器内部,包含了40 kHz低速内部RC振荡电路LSE。

但是,其精准度不是很高,本系统又增加了32.768 kHz的晶振电路驱动RTC实时时钟。外围电路增加纽扣电池即可长时间工作。

评论