基于DSP语音识别系统的硬件设计

摘要:语音识别是当前研究热点之一,应用十分广泛。系统浮点运算量很大,所以采用浮点型DSP。文章主要研究以DSP处理器为核心的硬件系统,包括电源电路,复位电路,时钟电路,JTAG接口电路,外部存储电路和语音处理电路等,并对每个电路模块进行详细的阐述。该方案已经可以作为模板电路实现。

关键词:DSP;TMS320C6713;硬件设计;语音识别

0 引言

随着超大规模集成电路和数字信号处理(DSP)的快速发展,DSP应用越来越广泛,涉及到各个领域如语音处理,图像处理等方面。现在语音识别中许多复杂算法已经能够在硬件上实现。最近十多年来,己研发出不少应用于不同领域的便携式语音识别系统。DSP处理速度快、灵活、精确,满足了对信号快速、实时、精确处理的要求,所以很适用于语音识别。

1 系统硬件设计

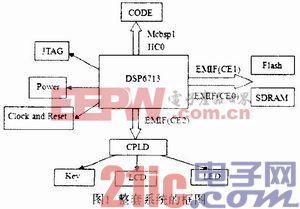

本文所提出的语音识别系统硬件电路是以最小系统板为基础,系统所要完成的主要功能包括:进行基本信号采集、数据运算及数据、程序存储;音频信号的采集、处理及输入、输出;与主机间的通信及数据、程序传输,同时配备了外部扩展接口,方便对系统的功能扩展以实现更广泛的嵌入式应用。整套系统框图如图1所示。

1.1 电源电路

电源电路是整个电路的核心模块,C6000系列DSP采用的是双电源供电方式,即内核与I/O都需要供电。TMS320C6713BGDP300型DSP,其主频最高可达到300MHz,它对供电电压的要求是:内核电压(CVDD,core voltage)为1.26V,I/O电压(DVDD,device voltage)则与外部其他芯片相同,为3.3V。输入电压为5V,其中3.3V电压由LDO芯片TPS75801来产生,1.26V由DC/DC稳压芯片TPS54310产生。值得注意的是在加电过程中,要保证CVDD先得到供电,DVDD后得到供电,至少两者同时得到供电,间隔不得小于1s,否则会导致DSP不正常工作,甚至损坏器件。

1.2 复位电路

DSP6713需要系统在上电时为其提供一个100~200ms的复位脉冲,并且由于DSP6713的工作频率达到300MHz,在运行时很可能发生干扰和被干扰的现象,导致系统不稳定以致死机,所以需要自动复位电路具有监视功能。系统采用的是Maxim公司生产的MAX708监控器,它外围电路简单,能有效提高系统的可靠性和抗干扰能力。

1.3 时钟电路

C6713时钟由外部引脚CLKIN输入,采用25 MHz有源晶振,通过内部PLL来分频产生SYSCLK1(core),SYSCLK2(Peripherals),SYSCLK3给各个模块提供时钟,并产生ECLKOUT来给EMIF提供时钟。由于CPLD可能需要不同的几个时钟输入,所以将25MHz有源晶振通过一个时钟乘数器ICS512将时钟频率加倍,产生不同的时钟供CPLD使用。

1.4 JTAG电路

仿真器的JTAG接口都满足IEEE 1149.1标准,与仿真器上的接口一致。系统采用标准的14脚接口,需要注意的是EMU0和EMU1需要加上拉电阻。

1.5 音频电路

音频采集采用TLV320AIC23实现输入和输出,与DSP的接口有2个,一个用于控制,一个用于数据传输。其中控制接口通过IIc0接口与DSP通信,数据接口通过Mcbsp1来与DSP通信,实现无缝连接。

1.6 SDRAMFlash

SDRAMFlash都由EMIF接口引出,SDRAM用于存储大量的数据,映射到CE0空间,字节地址从0x8000 0000开始,Flash用于bootloader程序,映射于CE1空间,字节地址从0x9000 0000开始。其中还涉及到地址偏移的问题,因为6713EMIF接口支持8/16/32位的不同存储器接口,存在物理地址和逻辑地址的偏移问题。

1.7 CPLD电路

由于DSP的管脚都是复用的,并且具有特殊功能,如果将LCD显示屏和按键直接与DSP相连会造成资源的浪费,所以使用CPLD来扩展系统所需的一些外扩接口,包括LCD显示屏、按键、LCD等。CPLD采用epm240系列的芯片,DSP的ECLKOUT或者外部输入时钟给CPLD提供时钟信号。DSP的5根地址线(A2~A6)和8根数据线(D0~D7)与CPLD的IO口相连,通过译码来创建用户所需要的的寄存器,每个寄存器都有相对应的地址,可在DSP程序中直接对其进行赋值。CPLD映射于CE2空间中,地址从0xA000 0000开始。

2 结语

浮点DSP芯片由于其出色的运算能力和非常高的运行速度,特别适合用于语音识别场合。硬件电路是DSP语音识别系统的核心部分,它的好坏直接影响到最后识别的结果。作为以DSP芯片为核心的高频数据处理模块,在进行PCB设计时更是要谨慎。尤其是高频部分,走线的好坏对数据传输起到很关键的作用,如SDRAM部分,其数据线和地址线要做到等长处理,还要加33 Ω电阻以防止信号的反射。为了滤除噪声,提高系统稳定性,还需要在DSP附近加60个左右0402封装的去耦电容。

评论