TSMC确认采用Cadence 3D-IC技术应用于其CoWoS参考流程

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),今天宣布TSMC已经确认采用Cadence 3D-IC技术应用于其CoWoS (chip-on-wafer-on-substrate)参考流程,用来开发CoWoS?测试载具,包含一个SoC与Cadence Wide I/O存储器控制器与PHY IP。这是晶圆厂方面的首个硅验证的参考流程,可用于多晶粒集成,并包含TSMC CoWoS?与Cadence 3D-IC技术,使得3D-IC设计成为电子公司的可靠选择。

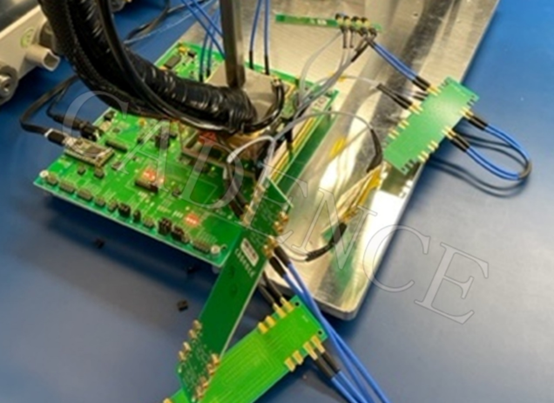

本文引用地址:http://www.eepw.com.cn/article/137868.htm3D-IC解决方案中经检验的可靠技术涵盖Cadence Encounter? RTL-to-signoff和Virtuoso?定制/模拟平台。同样包含于其中的还有Cadnece系统级封装产品,以及最近刚收购的Sigrity电源感知芯片/封装/电路板信号完整性解决方案,帮助工程师攻克从规划到实现、测试、分析和验证的整个过程中的晶粒堆叠与硅载体问题,。TSMC独特的CoWoS?组合凸块单元可以简化凸块分配,目前在Cadence Encounter Digital Implementation(EDI)System、QRC Extraction和Cadence Physical Verification System中自动获得支持。CoWoS?参考流程有CoWoS?设计工具包可用,以及从TSMC测试载具获得硅验证结果。

TSMC 选择Cadence的高带宽、低功耗 Wide I/O控制器与PHY设计IP解决方案,使用CoWoS?技术连接SoC与Wide I/O DRAM,其存储器界面的峰值数据率超过100Gbit/Sec。

3D-IC技术为工程师开发当今复杂设计提供了多种主要优势,包括更高的性能,降低的功耗,以及更小的体积。TSMC的CoWoS?是一种综合的工艺技术,将多个芯片捆绑在单个设备里,降低功耗与体积,同时提升系统性能。Cadence 3D-IC技术可以帮助数字、定制与封装环境之间的多芯片协同设计,在各芯片与硅载体上都采用了硅通孔技术(TSV),并支持微型凸块排列、布置、布线、可测性设计以及从系统的角度进行分析与验证。Wide I/O控制器与PHY展示了在3D-IC技术上应用存储器子系统的优势,大幅降低运作功率,提高存储器带宽。

“Cadence 3D-IC技术助力新一代高性能移动设备,并提供了系统性能与功率效率方面的极大优势,”Cadence硅实现部门研发部高级副总裁Chi-ping Hsu说,“我们继续与TSMC在CoWoS?工艺上进行合作,确保此底层技术能够继续支持重要的新兴技术。”

“TSMC继续与Cadence紧密合作,在业界推广3D-IC技术,”TSMC设计底层技术营销部门高级主管Suk Lee说,“我们已经花了三年时间与OIP产业链的合作伙伴一起准备CoWoS?设计流程用于生产,现在我们已经做好准备帮助客户用TSMC CoWoS?技术进行3D-IC设计。”

评论