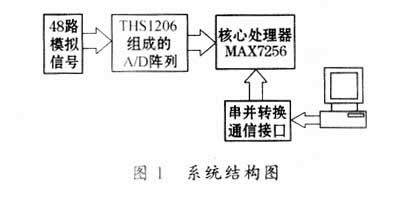

- 摘 要:本文介绍了一种基于PCI总线的高速实时数据采集系统的设计与实现方法,主要讨论了高速数据采集的存储与传输的硬件解决方案,以及该系统的控制逻辑的实现,最后给出了控制逻辑仿真波形。关键词:PCI总线;CPCI总线;高速实时数据采集;FIFO;CPLD

引言目前的大多数雷达信号处理机都是采用自定义总线,不具有通用性,每进行一些系统功能的改变就需要大量的硬件改动。而CPCI总线作为一种新兴的工业总线,其采用了PCI总线的电气特性以及VME总线的物理特性,兼具了二者的优点

- 关键字:

CPCI总线 CPLD FIFO PCI总线 高速实时数据采集

- 摘 要:本文介绍了可编程定时器/计数器8253的基本功能,以及一种用VHDL语言设计可编程定时器/计数器8253的方法,详述了其原理和设计思想,并利用Altera公司的FPGA器件ACEX 1K予以实现。关键词:FPGA;IP;VHDL

引言在工程上及控制系统中,常常要求有一些实时时钟,以实现定时或延时控制,如定时中断,定时检测,定时扫描等,还要求有计数器能对外部事件计数。要实现定时或延时控制,有三种主要方法:软件定时、不可编程的硬件定时、可编程的硬件定时器。其中可编

- 关键字:

FPGA IP VHDL

- 摘要:本文给出了一个基于CPLD高速超声车距报警器系统设计。关键词:车距报警器;CPLD;双口RAM 引言 为减少汽车碰撞事故的发生,汽车碰撞技术在近年发展很快。汽车避撞技术首先需要解决的问题是汽车之间的安全距离,当汽车与汽车之间的距离小于安全距离时,就应该能够自动报警。本文给出了高速防撞器的核心部分:车距报警器的设计方法。笔者设计了一款安装于车前/车尾的便携式系统,能在汽车停车、倒车以及行使过程中自动监控汽车与其它汽车、人和障碍物之间的距离,如果距离小于规定的安全距离

- 关键字:

CPLD

- 摘 要:本文介绍了应用于磁轴承的双DSP热备容错控制方案,该方案采用时钟同步技术,由总线表决模块实现系统的容错处理,硬件判决模块实现硬件故障判断。由中心仲裁模块根据两判决模块的结果进行复杂的仲裁,并完成切换和完善的报警逻辑,从而提高了磁轴承控制系统的可靠性。关键词:容错;磁轴承; 控制器; CPLD; DSP引言电磁轴承(AMB)是利用可控电磁吸力将转子悬浮起来的一种新型高性能轴承,具有无接触、无摩擦、高速度、高精度、不需润滑和密封等一系列特点,在交通、超高速超精密加工

- 关键字:

CPLD DSP 磁轴承 控制器 容错

- 摘 要:本文介绍了基于PCI专用芯片PCI9054和CPLD的DVB码流接收系统的硬件设计。该设计采用了PCI9054+CPLD的数字处理方案,并采用一种新的方法更高效地利用双端口RAM,保证了高速、大容量数据流的实时处理。关键词:DVB;PCI;CPLD;双端口RAM;WDM模式 前言通过PC接收DVB(数字视频广播)码流已成为一项新的多媒体数据接收技术。因此,设计基于PC平台的DVB码流接收卡,是数字广播电视发展的需要。由于DVB传输流的平均传输速率为6

- 关键字:

CPLD DVB PCI WDM模式 双端口RAM 存储器

- 摘 要:本文在分析了非对称同步FIFO的结构特点及其设计难点的基础上,采用VHDL描述语言,并结合FPGA,实现了一种非对称同步FIFO的设计。关键词:非对称同步FIFO;VHDL;FPGA;DLL;BlockRAM引言FIFO是一种常用于数据缓存的电路器件,可应用于包括高速数据采集、多处理器接口和通信中的高速缓冲等各种领域。然而在某些应用,例如在某数据采集和处理系统中,需要通过同步FIFO来连接8位A/D和16位数据总线的MCU,但是由于目前同步FIFO器件的输入与输

- 关键字:

BlockRAM DLL FPGA VHDL 非对称同步FIFO 存储器

- 摘 要:本文提出了一种利用边沿触发鉴相缩短锁相环捕获时间的方案,并详细介绍了该方案基于FPGA的实现方法。通过对所设计的锁相环进行计算机仿真和硬件测试,表明该方案确实可以提高锁相环的捕获性能。关键词:数字锁相环(DPLL);捕获时间;FPGA;VHDL引言捕获时间是锁相环的一个重要参数,指的是锁相环从起始状态到达锁定状态所需时间。在一些系统中,如跳频通信系统,由于系统工作频率不断地发生快速变化(每秒几百次到几千次,甚至高达上万次),要求锁相环能够对信号相位快速捕获。因此

- 关键字:

FPGA VHDL 捕获时间 数字锁相环(DPLL)

- 摘 要:本文根据Gollmann密钥流发生器的原理和伪随机序列产生的程序,利用VHDL语言和CPLD,设计出Gollmann密钥流发生器。该发生器满足一般的加密要求,可以保护信息传输的安全。关键词:Gollmann ;VHDL ;CPLD;伪随机序列引言对通信数据进行加密的方法可分为两大类:软加密和硬加密。其中硬加密具有加密强度大、可靠性高等特点。本文根据流密码发生器原理,用CPLD设计出了Gollmann流密码发生器。原理密码安全的伪随机序列发生器用于流密码时十分理想

- 关键字:

CPLD Gollmann VHDL 伪随机序列

- 介绍一种利用微控制器动态配置CPLD器件的方法。将配置文件存放在存储器中,配置文件中的控制代码驱动在微处理器中运行的配置引擎;将配置文件中的配置信息通过JTAG口移入CPLD,实现器件的动态配置

- 关键字:

CPLD 器件 动态配置 系统

- 摘 要:本文介绍了一种同步测周期计数器的设计,并基于该计数器设计了一个高精度的数字频率计。文中给出了计数器的VHDL编码,并对频率计的FPGA实现进行了仿真验证,给出了测试结果。关键词:频率计;VHDL;FPGA;周期测量

在现代数字电路设计中,采用FPGA结合硬件描述语言VHDL可以设计出各种复杂的时序和逻辑电路,具有设计灵活、可编程、高性能等优点。本文将介绍一种基于FPGA,采用同步测周期的方法来实现宽频段高精度数字频率计的设计。

图1 同步测周期计数器

- 关键字:

FPGA VHDL 频率计 周期测量

- 较详细地阐述不同逻辑电平的接口原理。以低压CPLD EPM7512A为例,给出在混合电压系统中的具体设计方案。

- 关键字:

7512A CPLD 7512 EPM

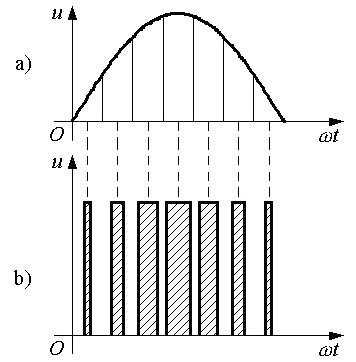

- 介绍了基于可编程逻辑器件CPLD和直接数字频率合成技术(DDS)的三相多波形函数发生器的基本原理,并在此基础上给出了基于CPLD的各模块设计方法及其VHDL源程序。

- 关键字:

CPLD 三相 多波形 函数发生器

- 采用VHDL语言和图形输入设计方法,给出了用CPLD在远程多路数据采集系统中实现地址译码、串口扩展、模块测试、模数转换以及高位数据处理等功能的具体方法,同时简要介绍了远程多路数据采集系统的工作原理及软、硬件框架。

- 关键字:

CPLD 远程 多路数据采集 系统

vhdl-cpld介绍

您好,目前还没有人创建词条vhdl-cpld!

欢迎您创建该词条,阐述对vhdl-cpld的理解,并与今后在此搜索vhdl-cpld的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473