引 言

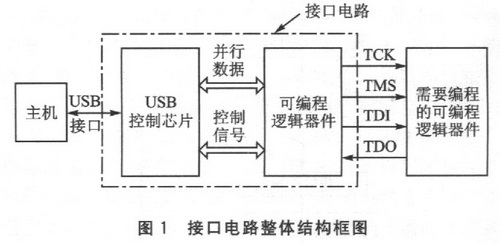

随着片上系统(SoC,System on Chip)时代的到来,包括复杂可编程逻辑器件(CPLD,Complex ProgrammableLogic Devi(e)和现场可编程门阵列(FPGA,Field Programmable Gate Array)的可编程逻辑器件(具有在系统可再编程的独特优点),应用越来越广泛。这给用于可编程逻辑器件编程的下载电缆提出了更高的要求。

本文研究基于IEEEll49.1标准的USB下载接口电路的设计及实现。针对Altera公司的FPGA器件Cy-

关键字:

CPLD USB FPGA 下载电缆 SoC

0 引言

数字图象处理技术在电子通信与信息处理领域得到了广泛的应用,设计一种功能灵活、使用方便、便于嵌入到系统中的视频信号采集电路具有重要的实用意义。

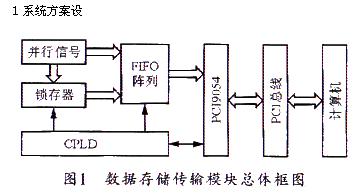

在研究基于DSP的视频监控系统时,考虑到高速实时处理及实用化两方面的具体要求,需要开发一种具有高速、高集成度等特点的视频图象信号采集系统,为此系统采用专用视频解码芯片和复杂可编程逻辑器件(CPLD)构成前端图象采集部分。设计上采用专用视频解码芯片,以CPLD器件作为控制单元和外围接口,以FIFO为缓存结构,能够有效地实现视频信号的采集与读取

关键字:

DSP 数据采集 视频采集 CPLD 数字图象处理

一种基于视频解码芯片与CPLD的实时图像采集系统,采用视频解码芯片SAA7114H进行A/D转换,在CPLD芯片XC95216的逻辑控制下通过乒乓缓存技术进行数据存储。

关键字:

CPLD 视频解码芯片 实时图像 采集系统

步进电机是一种将脉冲信号转换成角位移的伺服执行器件。其特点是结构简单、运行可靠、控制方便。

尤其是步距值不受电压、温度的变化的影响、误差不会长期积累,这给实际的应用带来了很大的方便。它广泛用于消费类产品(打印机、照相机)、工业控制(数控机床、工业机器人)、医疗器械等机电产品中。

通常的步进电机控制方法是采用CPU(PC

关键字:

单片机 CPLD 步进电机

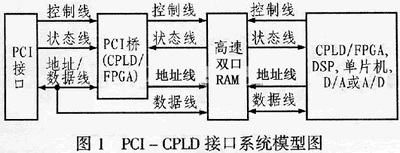

用CPLD设计所构成的CPI接口系统具有简洁、可靠等优点,是一种行之有效的设计途径。很多技术杂志和网站上,都有不少用CPLD设计PCI常规传输系统的文章。但用这些方法在MzxPlusII、Fundition等环境下进行模拟仿真时,其产生的时序往往与PCI规范有很大出入。虽然 Altera 等公司推出PCI核可以直接使用,但这样的内核占用CPLD资源较多,且能适配的器件种类少,同时价格也高,在实际设计应用中有很大的局限性。因此,使用通用型CPLD器件设计简易型PCI接口有很大的现实意义。在Compact

关键字:

VHDL-CPLD

摘要:

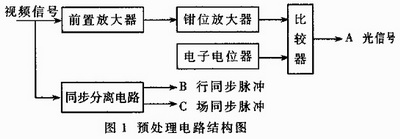

介绍了一种采用视频方式的点坐标测量方法。方案设计巧妙,测量方法稳定了可靠、精度高。该方法采用CCD摄像头拍摄屏幕画面获取光点信号,对摄像头输出的视频信号经过处理后,得到需要的一系列数字信号,然后在CPLD中完成数字逻辑功能,最终得到点的坐标。

测量一幅画面中某点的坐标,大多采用人工方法。但在有些工作条件下,这种方法给工作人员带来不便。本文介绍一种自动测量点坐标的实现方案。

1 系统总体设计方案

该方案测量对象是光点,在实验中用红色激光笔产生,使用加入红色滤光片的CCD摄

关键字:

CPLD

引言

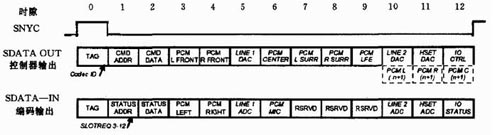

数字音频处理是指为真实再现声音的逼真效果而对音频进行的编解码处理技术,它是宽带网络多媒体、移动多媒体通信的关键技术.Audio Codec′97(音频数字信号编/解码器)是其中一种用于声音录放的技术标准,简称AC′97. AC′97采用双集成结构,即Digital Controller(数字信号控制器)和Audio Codec(音频编解码),使模/数转换器ADC和数?模转换器DAC转换模块独立,尽可能降低EMI(电磁干扰)的影响。

利用FPGA,可

关键字:

FPGA VHDL

提出一种利用FPGA实现AC-Link数字音频处理的设计方案.AC-Link音频编解码系统以VHDL模块进行设计,经过波形仿真和结果验证后,将程序下载到FPGA中实现1这种设计方法可以缩短设计周期,提高设计的可靠性和效率。

引言

数字音频处理是指为真

关键字:

AC-Link VHDL FPGA

l 引言

利用硬件描述语言结合可编程逻辑器件(PLD)可以极大地方便数字集成电路的设计,本文介绍一种利用VHDL硬件描述语言结合现场可编程门阵列(FPGA)设计的数控延时器,延时器在时钟clk的作用下,从8位数据线输入延时量,到LATCH高电平时锁存数据,可以实现对触发脉冲TRIG的任意量的延时。由于延时范围不同,设计所用到的FPGA的资源也不同,本文详细介绍最大延时量小于触发脉冲周期的情况。该延时器的软件编程和调试均在MuxplusⅡ环境下完成,系统设计选用Altera公司的EPFl0K30A

关键字:

VHDL 现场可编程门阵列

VHDL是随着可编辑逻辑器件(PLD)的发展而发展起来的一种硬件描述语言。它是1980年美国国防部VHSIC(超高速集成电路)计划的一部分,并于1986年和1987年分别成为美国国防部和IEEE的工业标准。作为一种硬件设计时采用的标准语言,VHDL具有极强的描述能力,能支持系统行为级、寄存器传输级和门级三个不同层次的设计,这样设计师将在TOP-DOWN设计的全过程中均可方便地使用同一种语言。而且,VHDL设计是一种“概念驱动式”的高层设计技术,设计人员毋需通过门级原理图描述电路

关键字:

VHDL

1.引言

可编程逻辑器件PLD(Programmable logic Device)就是由用户进行编程实现所需逻辑功能的数字专用集成电路ASIC。可编程逻辑器件在现代电子工程设计中得到了广泛应用。它是在PAL,GAL等逻辑器件的基础上发展起来的,具有高密度,高速度,低功耗体系结构和逻辑单元,灵活以及运用范围宽等特点,同时还具有设计周期短,制造成本低,开发工具先进,标准产品无需测试,质量稳定及可实时布线检验等优点。

现场总线技术广泛应用于工业和军用测控局域网中,它可以实现较远距离、较快速度的

关键字:

CPLD

声发射技术是光纤传感技术和声发射技术相结合的产物,是目前声发射技术的发展趋势。它将高灵敏度声发射传感器安装于受力构件表面以形成一定数目的传感器阵列,实时接收和采集来自于材料缺陷的声发射信号,进而通过对这些声发射信号的识别、判断和分析来对材料损伤缺陷进行检测研究并对构件强度、损伤、寿命等进行分析和研究。

在实际的构件检测中,现场声源信号通常是在100~800 khz之间的微弱高频信号,而且材料损伤检测、声发射源定位往往需要多个传感器形成传感器阵列,而声发射信号的数据传输系统必须达到640 mbps

关键字:

CPLD 信号

详细讨论了在MAX plusⅡ开发平台下使用VHDL硬件描述语言设计现场可编程门阵列(FP-GA)时常见的三个问题:等占空比分频电路、延时任意量的延时电路、双向电路。

1 引言

随着EDA技术的发展,使用硬件语言设计可编程逻辑器件(PLD)/现场可编程门阵

关键字:

VHDL FPGA 问题

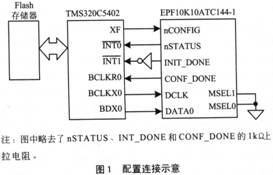

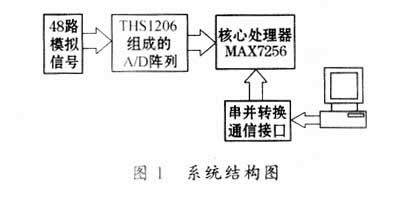

1 总体描述

系统中的DSP采用TI公司的定点数字信号处理器TMS320C5402。它采用4总线4级流水线的增强型哈佛结构,处理速度为100MIPS;具有片内4K×16位的ROM和16K×16位的DARAM, 2个多通道缓冲串行口(McBSP),1个直接存储控制器(DMA)等片内外围电路;外部可扩展至1M×16位存储空间,芯片采用3.3V电源电压。

TMS320C5402的多通道缓冲串行口(mu

关键字:

DSP CPLD

vhdl-cpld介绍

您好,目前还没有人创建词条vhdl-cpld!

欢迎您创建该词条,阐述对vhdl-cpld的理解,并与今后在此搜索vhdl-cpld的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473