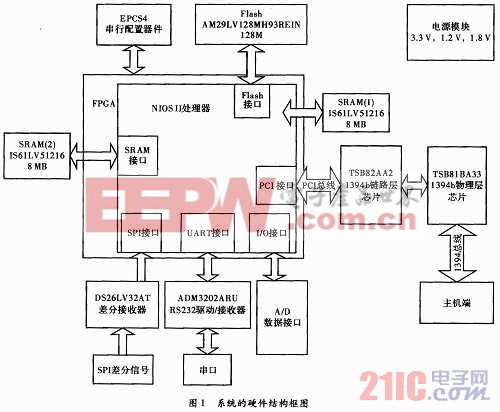

- 摘要:介绍了IEEE 1394h串行总线的特点,并以FPGA嵌入式处理器Nios II为控制核心,设计实现了一种1394b高速数据传输系统。阐述了该系统的硬件设计和软件工作流程。实验表明,该系统可靠性高、实时性好、具有广泛的应

- 关键字:

1394b FPGA IEEE 高速数据

- ST-BUS总线接口模块的Verilog HDL设计,ST-BUS是广泛应用于E1通信设备内部的一种模块间通信总线。结合某专用通信系统E1接口转换板的设计,本文对ST-BUS总线进行了介绍,讨论了ST-BUS总线接口收发模块的设计方法,给出了Verilog HDL实现和模块的时序仿真图。

- 关键字:

HDL 设计 Verilog 模块 总线 接口 ST-BUS

- 日本的机器人专家计划使用KOHGA3地面机器人在日本本州岛东北部八户地区的一座坍塌的大楼里进行侦测。(图中所示是正在测试中的机器人)。

在日本仙台发生9级大地震之后,日本投入使用更多的机器人协助搜救和复原工作。

我们此前报导过,两支救援队正在整装待发,准备部署地面机器人和蛇形机器人。一支救援队位于东京,另一救援队位于仙台,并且他们准备在必要时到达日本任何地区参与搜救。

现在,我们了解到,另外两支救援队也准备使用机器人。一队由千叶理工学院的Eiji Koyanagi教授率领,他们是应位

- 关键字:

IEEE 机器人

- 随着IEEE Std 1394-1995技术的高速发展,IEEE 1394已经成为众多电子设备基本的外部接口。然而,要进一步扩展它的适用领域,就必须克服其接口被限制工作在较短距离以及不适用于较高数据传输率的缺陷。IEEE Std 1394

- 关键字:

FPGA 1394 IEEE 数据传输

- 摘要:基于FPGA内嵌的NIOSII处理器,设计了一个1394b双向数据传输系统。介绍了该系统的硬件结构,描述了其软件工作流程,主要包括异步传输和等时传输的具体实现过程。测试结果表明,该系统的传输速率较高、可靠性和实

- 关键字:

数据 传输系统 双向 IEEE-1394 NlOSII 处理器 基于

- verilog中阻塞赋值和非阻塞赋值,阻塞和非阻塞语句作为verilog HDL语言的最大难点之一,一直困扰着FPGA设计者,即使是一个颇富经验的设计工程师,也很容易在这个点上犯下一些不必要的错误。阻塞和非阻塞可以说是血脉相连,但是又有着本质的差别。理解

- 关键字:

阻塞 verilog

- 今天我想和大家讨论一下基于IEEE802.15.4网络解决方案时系统构架的选项问题。凡事总有先后。如果...

- 关键字:

IEEE

- PLD/FPGA硬件语言设计verilog HDL,HDL概述 随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前最主要的硬件描述语言是VHDL和verilog HDL及System Verilog。 VHDL发展的较早,语法严格;而Verilog HDL是在C语言的基础上发展起来的一种硬

- 关键字:

verilog HDL 设计 语言 硬件 PLD/FPGA

- Verilog HDL与VHDL及FPGA的比较分析, Verilog HDL 优点:类似C语言,上手容易,灵活。大小写敏感。在写激励和建模方面有优势。 缺点:很多错误在编译的时候不能被发现。 VHDL 优点:语法严谨,层次结构清晰。 缺点:熟悉时间长,不够灵

- 关键字:

比较 分析 FPGA VHDL HDL Verilog

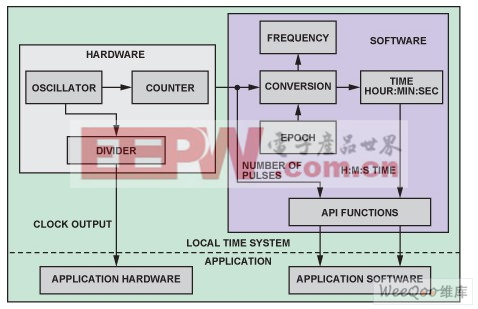

- 利用IEEE 1588和Blackfin嵌入式处理器实现设备时钟同步,本文介绍原版IEEE 1588-2002标准以及更新版本IEEE 1588-2008中的改进内容。由于IEEE 1588在一些目标应用中越来越重要,因此ADSP-BF518 Blackfin嵌入式处理器中也集成专用硬件来支持IEEE 1588。本文将概要介绍其功能,并通过一个示例来展示利用ADSP-BF518处理器解决方案获得的时钟同步性能结果。

- 关键字:

设备 时钟 同步 实现 处理器 IEEE Blackfin 嵌入式 利用

- 基于FPGA和硬件描述语言Verilog的液晶显示控制器的设计,本设计是一种基于FPGA(现场可编程门阵列)的液晶显示控制器。与集成电路控制器相比,FPGA更加灵活,可以针对小同的液晶显示模块更改时序信号和显示数据。FPGA的集成度、复杂度和面积优势使得其日益成为一种颇具吸引力

- 关键字:

液晶显示 控制器 设计 Verilog 语言 FPGA 硬件 描述 基于

- 提出了使用正交频分复用(OFDM)技术减少码间干扰(ISI)来改善频率选择性衰落信道下空时编码(STC)性能的合理方案。在IEEE802.11a无线标准下对STC与OFDM技术相结合后的STC-OFDM系统进行了理论分析,通过仿真对系统性能进行了评估。仿真结果表明,空时分组编码(STBC)与OFDM技术的结合优于垂直的贝尔实验室分层空时方案(VBLAST)与OFDM技术的结合;FFT点数与子载波数对系统性能有一定的影响;随机交织器有助于显著改善多径衰落信道下系统性能,并能在各种信道上达到合理的鲁棒性。

- 关键字:

STC-OFDM 802.11 IEEE 无线标准

verilog-ieee介绍

您好,目前还没有人创建词条verilog-ieee!

欢迎您创建该词条,阐述对verilog-ieee的理解,并与今后在此搜索verilog-ieee的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473