“FPGA目前非常火,各个高校也开了FPGA的课程,但是FPGA并不是每个人都适合,FPGA讲究的是一个入道,入什么道,入电子设计的道,就是说,这个过程,你得从电子设计开始,然后再学FPGA,而不是先从VHDL/Verilog开始,直接跳过数电模电。这一点非常重要,这涉及到你以后的发展高度的问题。我是过来人,我深刻体会到FPGA与数电模电的基础的深层次联系。对于本科生而言,你可以把FPGA当作业余兴趣,但不要把它当成今后的饭碗,你可以保持这个兴趣直到研究生读完。从我招聘的情况来看,做FPG

关键字:

FPGA Verilog SRAM

引言

数字滤波器是语音与图像处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件, 它能满足波器对幅度和相位特性的严格要求, 避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。

1 FIR 数字滤波器

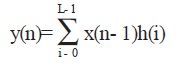

FIR 滤波器用当前和过去输入样值的加权和来形成它的输出, 如下所示的前馈差分方程所描述的。

FIR 滤波器又称为移动均值滤波器, 因为任何时间点的输出

关键字:

Verilog 数字滤波器

引言

数字滤波器是语音与图像处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件, 它能满足波器对幅度和相位特性的严格要求, 避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。

1 FIR 数字滤波器

FIR 滤波器用当前和过去输入样值的加权和来形成它的输出, 如下所示的前馈差分方程所描述的。

FIR 滤波器又称为移动均值滤波器, 因为任何时间点的输出

关键字:

Verilog FIR 数字滤波器

9、关于任务和函数的小结,挑几点重要的说一下吧

(1)任务具有多个输入、输入/输出和输出变量,在任务重可以使用延迟、事件和时序控制结构,在任务重可以调用其它任务和函数。与任务不同,函数具有返回值,而且至少要有一个输入变量,而且在函数中不能使用延迟、事件和时序控制结构,函数可以条用函数,但是不能调用任务。

(2)在声明函数时,系统会自动的生成一个寄存器变量,函数的返回值通过这个寄存器返回到调用处。

(3)函数和任务都包含在设计层次中,可以通过层次名对他们实行调用。这句话什么意思啊?

关键字:

FPGA Verilog

我们接着上篇文章继续学习,上次提到了两种赋值语句,让我们接着往下学。

1、块语句

块语句包括两种,一个是顺序块,一个是并行块。

(1)顺序快

顺序快就好比C语言里的大括号“{ }”,在Verilog语法中,用begin…end代替。这里只需要知道,在begin…end中间的语句是顺序执行的就行了。

(2)并行块

并行块可以算是一个新的知识点,与顺序块最大的不同就是并行块中的语句是同时开始执行的,要想控制语句的先后顺

关键字:

FPGA Verilog

这几天复习了一下Verilog的语法知识,就借此写写我对这些东西的想法吧。感觉呢,是和C语言差不多,具有C语言基础的朋友学起来应该没什么问题,和C语言相同的地方就不说了吧,重点说一下不同点吧。

1、模块的结构

模块呢,是Verilog的基本设计单元,它主要是由两部分组成,一个是接口,另一个是逻辑。下面举一个小例子说明一下:

module xiaomo (a,b,c,d);

input a,b;

output c,d;

assign c=a|b;

assign

关键字:

FPGA Verilog

入门前

刚才开始接触逻辑设计很多人会觉得很简单:因为verilog的语法不多,半天就可以把书看完了。但是很快许多人就发现这个想法是错误的,他们经常埋怨综合器怎么和自己的想法差别这么大:它竟然连用for循环写的一个计数器都不认识!

相信上一段的经历大部分人都曾有,原因是做逻辑设计的思维和做软件的很不相同,我们需要从电路的角度去考虑问题。

在这个过程中首先要明白的是软件设计和逻辑设计的不同,并理解什么是硬件意识。

软件代码的执行是一个顺序的过程,编绎以后的机器码放在存储器里,等着C

关键字:

逻辑设计 verilog D触发器

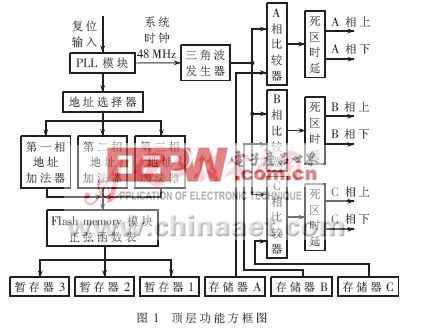

随着信号处理技术及集成电路制造工艺的不断发展,全数字化SPWM(正弦脉宽调制)算法在调速领域越来越受到青睐。实现SPWM控制算法的方法很多,其中模拟比较法因电路复杂、且不易与数字系统连接而很少采用;传统的微处理器因不能满足电机控制所要求的较高采样频率(≥1 kHz)而逐渐被高性能的DSP硬件系统所取代,但该系统成本高、设计复杂。与传统方法相比,在现场可编程逻辑器件FPGA上产生一种新的SPWM控制算法,具有成本低、研发周期短、执行速度高、可扩展能力强等优点。该技术进一步推动了变频调速技术的发展。

关键字:

Verilog HDL SPWM FPGA

作为一个负责FPGA 企业市场营销团队工作的人,我不得不说,由于在工艺技术方面的显著成就以及硅芯片设计领域的独创性,FPGA 正不断实现其支持片上系统设计的承诺。随着每一代新产品的推出,FPGA 在系统中具有越来来越多的功能,可作为协处理器、DSP 引擎以及通信平台等,在某些应用领域甚至还可用作完整的片上系统。 因此,在摩尔定律的作用下,FPGA 产业的门数量不断增加,性能与专门功能逐渐加强,使得 FPGA 在电子系统

关键字:

xilinx FPGA VHDL Verilog

由于Verilog HDL和 VHDL 行为描述用于综合的历史还只有短短的几年,可综合风格的Verilog HDL 和VHDL的语法只是它们各自语言的一个子集。又由于HDL的可综合性研究近年来非常活跃,可综合子集的国际标准目前尚未最后形

关键字:

Verilog HDL 进阶 代码

函数的目的是返回一个用于表达式的值。

关键字:

function Verilog HDL 函数

如果传给任务的变量值和任务完成后接收结果的变量已定义,就可以用一条语句启动任务。任务完成以后控制就传回启动过程。如任务内部有定时控制,则启动的时间可以与控制返回的时间不同。任务可以启动其他的任务,其他

关键字:

Verilog TASK HDL

task和function说明语句的区别task和function说明语句分别用来定义任务和函数。利用任务和函数可以把一个很大的程序模块分解成许多较小的任务和函数便于理解和调试。输入、输出和总线信号的值可以传入或传出任务和函

关键字:

function Verilog task HDL

实例的内容及目标1.实例的主要内容本节通过Verilog HDL语言编写一个具有“百分秒、秒、分”计时功能的数字跑表,可以实现一个小时以内精确至百分之一秒的计时。数字跑表的显示可以通过编写数码管显示程序来

关键字:

verilog HDL 基础教程 实例

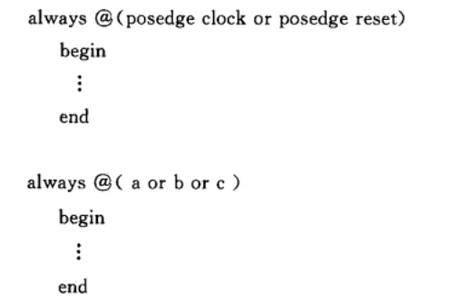

在Verilog HDL语言中,时序逻辑电路使用always语句块来实现。例如,实现一个带有异步复位信号的D触发器如下。例1:带异步复位的D触发器1。wire Din;wire clock,rst;reg Dout;always @ (posedge clock or negedge rs

关键字:

Verilog HDL 基础教程 时序逻辑电路

verilog-a介绍

您好,目前还没有人创建词条verilog-a!

欢迎您创建该词条,阐述对verilog-a的理解,并与今后在此搜索verilog-a的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473