- Verilog HDL的历史和进展 1.什么是Verilog HDLVerilog HDL是硬件描述语言的一种,用于数字电子系统设计。它允许设计者用它来进行各种级别的逻辑设计,可以用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是

- 关键字:

Verilog HDL 基础

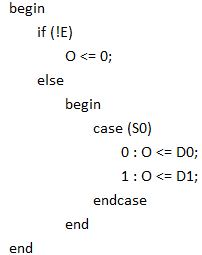

- 非阻塞赋值和阻塞赋值在Verilog HDL语言中,信号有两种赋值方式:非阻塞(Non_Blocking)赋值方式和阻塞(Blocking)赋值方式。(1)非阻塞赋值方式。典型语句:b = a;① 块结束后才完成赋值操作。② b的值并不是立刻就改

- 关键字:

Verilog HDL 基础教程

- 常用数据类型Verilog HDL中总共有19种数据类型,数据类型是用来表示数字电路硬件中的数据储存和传送元素的。在本书中,我们先只介绍4个最基本的数据类型,它们分别是:reg型,wire型,integer型和parameter型。其他

- 关键字:

Verilog HDL 基础教程 数据类型

- 实例的内容及目标 1.实例的主要训练内容本实例通过Verilog HDL语言设计一个简易的交通等控制器,实现一个具有两个方向、共8个灯并具有时间倒计时功能的交通灯功能。2.实例目标通过本实例,读者应达到下面的目标。掌握

- 关键字:

Verilog HDL 基础教程 实例

- Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言,也是一种结构描述的语言。也就是说,既可以用电路的功能描述,也可

- 关键字:

Verilog HDL 基础 程序

- 实例的内容及目标1.实例的主要内容本实例通过Verilog编程实现在红色飓风II代Xilinx开发板上面实现对键盘、LCD、RS-232等接口或者器件进行控制,将有键盘输入的数据在LCD上面显示出来,或者通过RS-232在PC机上的超级

- 关键字:

Verilog HDL PS 基础教程

- 数字逻辑电路分为两种,分别是组合逻辑与时序逻辑。(1)组合逻辑:输出只是当前输入逻辑电平的函数(有延时),与电路的原始状态无关的逻辑电路。也就是说,当输入信号中的任何一个发生变化时,输出都有可能会根据其变化

- 关键字:

Verilog HDL 基础教程 组合逻辑电路

- 数字电路设计工程师一般都学习过编程语言、数字逻辑基础、各种EDA软件工具的使用。就编程语言而言,国内外大多数学校都以C语言为标准,只有少部分学校使用Pascal 和Fortran。算法的描述和验证常用C语言来做。例如要

- 关键字:

Verilog HDL C语言 详解

- 对于Verilog HDL的初学者,经常会对语法中的几个容易混淆的地方产生困惑。下面列出几个常见问题和解决它们的小窍门。1.“=”和“=”的区分方法前面的内容已经从原理上解释了阻塞(=)和非阻塞(=

- 关键字:

Verilog HDL 家 程序设计

- Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言,也是一种结构描述的语言。也就是说,既可以用电路的功能描述,也可以

- 关键字:

Verilog HDL 基础教程 程序

- 本着方便后来人,不用那么苦逼的去看英文资料,可以更快的入门,同时也为了这接近一年的时间天天写Verilog作结,马上就要去上一年课了,不用再写代码,也不用再熬夜咯。为了方便阐述,以一个简单的8路选择器作为例子。

- 关键字:

ISE 8路选择器 Verilog 工程建立 入门 常见错误

- 从大学时代第一次接触FPGA至今已有10多年的时间。至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

- 关键字:

FPGA EDA VHDL Verilog 时钟 IP核

- 设计和实现了U盘SoC。本系统包括USB CORE和已验证过的CPU核、Nandflash、UDC_Control等模块,模块间通过总线进行通信。其中USB CORE为本文设计的重点,用Verilog HDL语言实现,同时并为此设计搭建了功能完备的Modelsim仿真环境,进行了仿真验证。

- 关键字:

U盘 片上系统 USB Verilog HDL

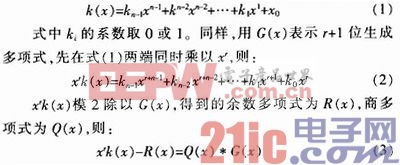

- 在介绍CRC校验原理和传统CRC32串行比特算法的基础上,由串行比特型算法推导出一种CRC32并行算法、并结合SATAⅡ协议的要求,完成了SATAⅡ主控制器设计中CRC生成与校验模块的设计。最后通过在ISE平台上编写Verilog硬件描述语言,对SATA协议中帧结构数据进行仿真,验证该CRC32并行算法能够满足SATA接口实时处理的要求。

- 关键字:

CRC32 并行算法 SATA Verilog

- 1 引言近30年来,由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA和嵌入系统的多种模式。可以说

- 关键字:

Verilog FPGA CPLD HDL

verilog-a介绍

您好,目前还没有人创建词条verilog-a!

欢迎您创建该词条,阐述对verilog-a的理解,并与今后在此搜索verilog-a的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473