全球领先的半导体设计、验证、和制造软件及知识产权 (IP) 的供应商新思科技有限公司(纳斯达克市场交易代码:SNPS)和中芯国际集成电路制造有限公司(中芯国际,纽约证券交易所交易代码:SMI,香港联交所交易代码:00981.HK)宣布已正式提供用于中芯国际先进65-nm 工艺的系统级芯片 (SoC) 综合设计解决方案。该解决方案将 Synopsys 丰富的 DesignWare? 接口、模拟 IP 产品组合和其他基础性 IP,通过可调参考流程与 Galaxy? 实现平台集成在一起。

关键字:

Synopsys SoC

全球半导体设计、验证及制造软件暨IP领导厂商新思科技(Synopsys)今日宣布,利用新思科技完整的DesignWare® SATA IP解决方案,包含控制器、实体层以及验证IP,使创意电子(Global Unichip Corp.) 之GP5080固态硬盘系统单芯片第一次流片就试产成功之成果。

系统单芯片设计代工服务的龙头企业创意电子,肯定了新思科技的DesignWare SATA IP在品质、功耗、性能和功能集上的卓越性。对创意电子来说SATA的互通性是一个关键的需求,而新思科技是唯

关键字:

Synopsys DesignWare IP

新思科技有限公司日前宣布:英飞凌科技(西安)有限公司通过采用新思完整的、基于统一功率格式(UPF)的低功耗综合、物理实现和验证流程,完成了国内首款采用40nm工艺技术的3G智能手机基带处理器设计,并按照时间计划成功实现一次流片成功。

为了达到芯片设计目标,英飞凌确定了在设计过程中采用了Synopsys全套实施流程,包括Design Compiler编译器、ICC布局工具等,同时引入新思的知识产权(IP)和支持服务。同时,还结合了英飞凌在移动通信基带芯片领域里丰富的经验和工程师的创新能力。

关键字:

Synopsys 40nm 基带处理器

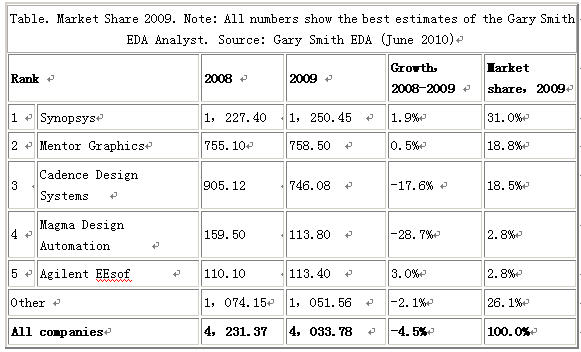

由Gary Smith的EDA小组及Nancy Wu与Marry Olsson共同编辑的市场统计已经完成。2009年最大的变化是Mentor超过Cadence成为EDA市场全球销售额依产品计的第二。这也意味着市场向ESL方法论过渡。Synopsys仍是首位。

Mentor在IC设计居第二。在兼并Valor后mentor成为PCB设计的第三。

在Walden Rhines的带领下当转向RTL设计方法时,相信近期Cadence已经停止它的市场份额下降,十分相似于Mentor的变化。

关键字:

Synopsys EDA

全球半导体设计制造软件和知识产权领先企业新思科技有限公司和全球领先的半导体制造商中芯国际集成电路有限公司今天宣布开始提供用于中芯国际65纳米(nanometer)低漏电(Low Leakage)工艺技术的新思科技经硅验证的和获得USB标志认证的DesignWare® USB 2.0 nanoPHY知识产权(IP)。作为一家提供包括控制器、PHY和验证IP等USB2.0接口完整IP解决方案的领先供应商,新思科技继续致力于通过提供高品质IP助力设计人员降低集成风险,这些IP具备了验证过的互操作性,

关键字:

Synopsys IP 65纳米 DesignWare

下一代系统提供最高的性能、最高的容量、预测试IP和独有先进验证功能

美国加利福尼亚州山景城,2010年5月—— 全球领先的半导体设计、验证和制造软件及知识产权(IP)供应商新思科技有限公司(Nasdaq:SNPS)今天宣布推出快速原型系统HAPS™-60系列,这是一种可降低复杂SoC设计和验证挑战的综合解决方案。HAPS-60系列是Confirma™ Rapid Prototyping Platform快速原型平台的一部分,是一种易于使用和具有高性价比的快

关键字:

Synopsys HAPS-60 SoC

Synopsys日前宣布,在其Galaxy设计实现平台中推出了最新的RTL综合工具Design Compiler 2010,它将综合和物理层实现流程增速了两倍。Design Compiler自1988年问世以来,随着工艺技术从1.5微米到32纳米的进步,而不断得到调整升级。而今时序与面积布线的优化已成为主要的挑战,最新版工具与时俱进,针对拓扑技术进行扩展,为Synopsys布局布线解决方案IC Compiler提供“物理层指引”;将时序和面积的一致性提升至5%的同时,还将IC

关键字:

Synopsys RTL 32纳米

全球领先的半导体设计、验证和制造的软件及知识产权(IP)供应商新思科技有限公司日前宣布:该公司在其Galaxy™设计实现平台中推出了最新的创新RTL综合工具Design Compiler 2010,它将综合和物理层实现流程增速了两倍。为了满足日益复杂的设计中极具挑战性的进度要求,工程师们需要一种RTL综合解决方案,使他们尽量减少重复工作并加速物理实现进程。为了应对这些挑战,Design Compiler 2010对拓扑技术进行扩展,为Synopsys旗舰布局布线解决方案IC Compile

关键字:

Synopsys Galaxy RTL

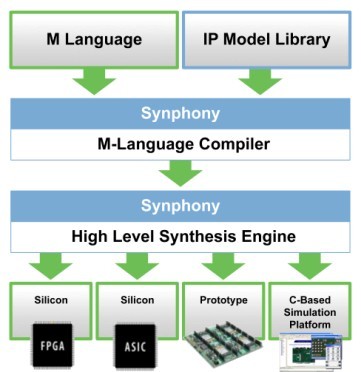

假如IC设计的速度能够加快数倍,那么拥有各种复杂功能的各类电子产品将再次改变我们的生活。

IC设计中设计与验证的流程通常需要数月甚至数年,其中的人工重新编码的过程费时且容易出错,Synopsys选择这一环节为突破,开发出了Synphony高层次综合EDA工具,通过其独特的MATLAB语言、基于模型的解决方案,针对ASIC和FPGA芯片设计实现了10倍的设计与验证能力。

据Synopsys公司总监Chris Eddington介绍,Synphony的创意来自被收购的Synplicity公司,

关键字:

Synopsys IC设计 EDA

全球领先的半导体设计、验证和制造软件、硬件及知识产权(IP)供应商新思科技公司(NASDAQ: SNPS),今天宣布推出其Synphony HLS (High Level Synthesis)解决方案。该解决方案集成了M语言和基于模型的综合法,与 传统RTL流程相比,能够为通信和多媒体应用提供高达10倍速的更高的设计和验证能力。Synphony HLS为ASIC 和 FPGA的应用、架构和快速原型生成最优化的RTL。此外,通过在虚拟平台中为系统验证和早期软件开发生成C模型,Synphony HLS补充

关键字:

Synopsys Synphony HLS

简·奥斯汀的《理智与情感》告诉我们,若要在地位和金钱都凌驾于爱情之上的社会得到幸福,一定要懂得在理智与情感之间取得平衡。对于在竞争激烈的科技领域驾御企业走向成功,同样不可缺少智慧和激情的平衡。近日,记者在北京采访了Synopsys公司董事长兼首席执行官Aart De Geus先生,这位一直强调以智慧和激情引领企业成功的商业奇才谈起了应对金融危机下的企业发展策略。

让De Geus先生可以坐在记者面前谈笑风生最重要的支撑就是Synopsys公司是在EDA行业中少数几个业绩预期继续增长

关键字:

Synopsys EDA IP 200907

全球领先的半导体设计与制造的软件和知识产权(IP)供应商新思科技(Nasdaq:SNPS)今天发布了VCS®功能验证解决方案...

关键字:

Synopsys VCS 新思科技 验证

全球领先半导体设计和制造软件及IP供应商Synopsys公司,今天宣布推出其扩展型Confirma™快速原型平台。通过引入最近收购的CHIPit®各种产品、工具和技术,简化了快速原型构建的实施和部署工作,确保用户可以更快地开始硬件辅助系统验证和嵌入式软件开发。再辅之以HAPS高性能原型硬件,扩展型Confirma平台现可同时提供软件可配置架构和基于事务的协同验证能力。Confirma平台结合了经过验证的原型方法、IP、服务、硬件和软件,对于多种原型应用来说都是一个全面的解决方案。S

关键字:

Synopsys Confirma

美国加利福尼亚州MOUNTAIN VIEW ,2009年2月9日—全球领先半导体设计和制造软件及IP供应商Synopsys公司(纳斯达克股票代码:SNPS),今天宣布推出其扩展型Confirma™快速原型平台。通过引入最近收购的CHIPit®各种产品、工具和技术,简化了快速原型构建的实施和部署工作,确保用户可以更快地开始硬件辅助系统验证和嵌入式软件开发。再辅之以HAPS高性能原型硬件,扩展型Confirma平台现可同时提供软件可配置架构和基于事务的协同验证能力。Conf

关键字:

Synopsys Confirma

Altera和Synopsys宣布,Altera流行的Nios II处理器内核可通过DesignWare Star IP包提供许可给客户使用。这一新品扩展了Altera现有的FPGA和HardCopy®结构化ASIC产品供给,帮助Nios II用户将设计移植到标准单元ASIC。Nios II处理器内核是应用最广泛的FPGA处理器,其客户群有5,000多家电子设备生产商,包括世界上排名靠前的OEM。

通过DesignWare Star IP包,设计人员可以使用一流Star IP供应商开发的

关键字:

嵌入式系统 单片机 Altera Synopsys Nios II MCU和嵌入式微处理器

synopsys.ai介绍

您好,目前还没有人创建词条synopsys.ai!

欢迎您创建该词条,阐述对synopsys.ai的理解,并与今后在此搜索synopsys.ai的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473