- 随着可编程逻辑器件的不断进步和发展,FPGA在嵌入式系统中发挥着越来越重要的作用。本文介绍的在电能质量监测系统中信号采集模块控制器的 IP核,是采用硬件描述语言来实现的。首先它是以ADS8364芯片为控制对象,结合实际电路,将6通道同步采样的16位数据存储到FIFO控制器。当FIFO 控制器存储一个周期的数据后,产生一个中断信号,由PowerPC对其进行高速读取。这样能够减轻CPU的负担,不需要频繁地对6通道的采样数据进行读取,节省了CPU运算资源。

1 ADS8364芯片的原理与具体应用

- 关键字:

FPGA 信号采集

- 赛灵思公司 (Xilinx+)日前宣布,其16nm UltraScale+™ 系列FPGA、3D IC和MPSoC凭借新型存储器、3D-on-3D和多处理SoC(MPSoC)技术,再次实现了领先的价值优势。此外,为实现更高的性能和集成度,UltraScale+系列还采用了全新的互联优化技术——SmartConnect。这些新的器件进一步扩展了赛灵思的UltraScale产品系列 (现从20nm 跨越至 16nm FPGA、SoC 和3D IC器件),同时利用台积电公

- 关键字:

赛灵思 FPGA SoC UltraScale 201503

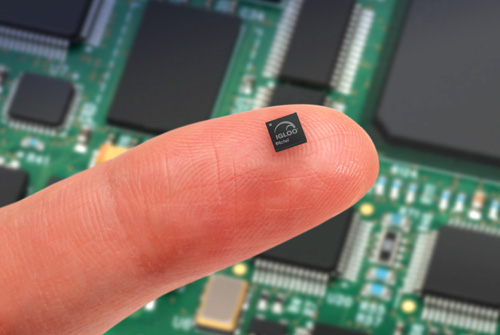

- 京微雅格(北京)科技有限公司(以下简称“京微雅格”)宣布将参加 3月 17 日至 19 日在上海举行的 2015慕尼黑上海电子展。活动期间,京微雅格将展示其FPGA产品在多个市场领域的应用方案,包括消费电子、智能家居、金融安全、机器人、物联网、汽车电子等。京微雅格展位号为半导体E3馆3646,诚邀您莅临参观。

图一:将在慕尼黑上海电子展期间现场展示的部分已量产芯片

FP

- 关键字:

京微雅格 FPGA

- 注:带“ * ”的表示选做,实际中根据时间和精力决定

基本外设的驱动开发:

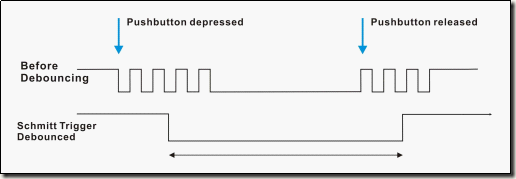

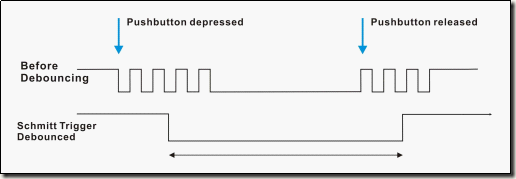

1. 独立按键消抖检测电路模块;

2. 4*4矩阵键盘消抖检测电路模块;

3. 7段8位数码管驱动电路模块;(直接FPGA驱动 和 外加74hc138译码器)

4. 二进制转BCD码模块设计;

5. uart串口收发电路模块;(verilog 和 VHDL)

6. IIC驱动电路模块;(暂时没定,会给出个24L64的驱动,也会开发一个传感器驱动)

7.

- 关键字:

FPGA 串口

- 本规范主要是对设计流程、端口名称、组织结构、文档编排进行约定。本约定作用仅仅是为了使后期代码设计和文档编写更加规范有序,方便自己和读者阅读,与公司的设计规范还差着十万八千里,因此,望大家万不可以小梅哥的规范作为标准。当然,小梅哥在规范约定时,也会尽量参考华为verilog规范和至芯科技的文档编写规范力争做到简洁通俗。

规范约定之设计文档基本结构

为了将设计能够清晰明了的介绍给大家,让大家一看就懂,文档编写时会详细包含以下内容:

一、 实验目的

二、 实验原理

三、 硬件设

- 关键字:

FPGA 状态机

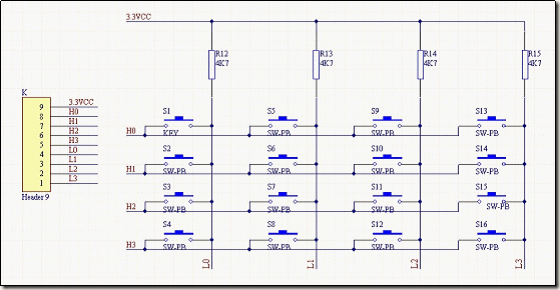

- 讲过了独立按键检测,理所当然应该讲讲FPGA中矩阵键盘的应用了。这个思维和电路在FPGA中有所不同,在此,在此做详细解释,Bingo用自己设计的成熟的代码作为案例,希望对你有用。

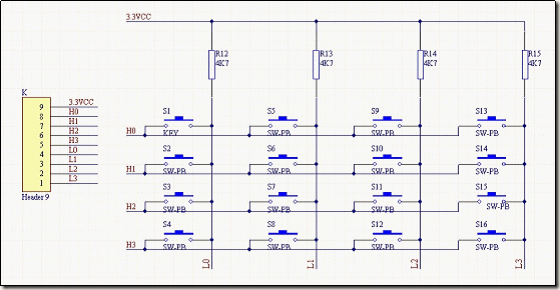

一、FPGA矩阵键盘电路图

在FPGA中的电路,与单片机雷同,如下所示:

在上电默认情况下,L[3:0] =4''b1,因为上拉了3.3V,而默认情况下H.[3:0]为低电平;一旦有某一个按键被按下,便是是的该路电路流向该按键的H,是的L检测不到电流。因此可以通过对每一行H输出的

- 关键字:

FPGA PLD

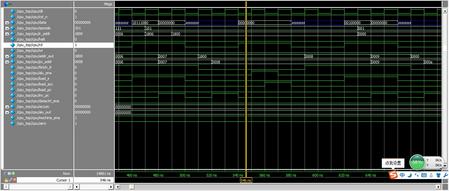

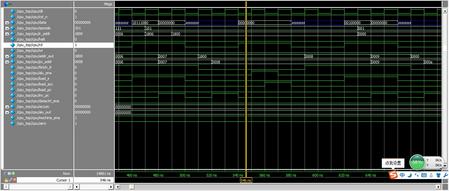

- 进入波形仿真后点击运行按钮即可出波形,下面我们来验证我们的cpu代码是否正确

大家先看两个图,等会小墨同学会结合这两个图给大家细细讲解仿真过程

我们先来看第一个过程

上电后,cpu先从ROM中读回两个周期的数据,是从ROM的0地址开始的,再对比我们之前定义好的ROM,数据读取正确,读回的数据的前三位是111,即指令码JMP,后13位003c为地址码,JMP指令是将读回的数据

- 关键字:

FPGA testbench

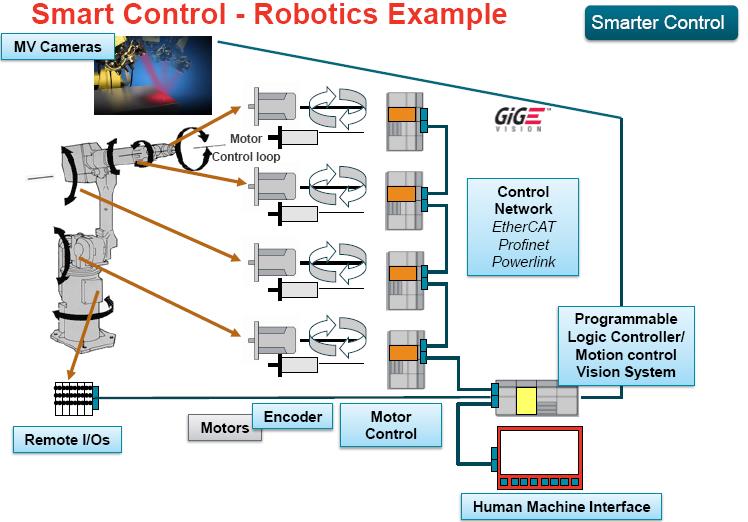

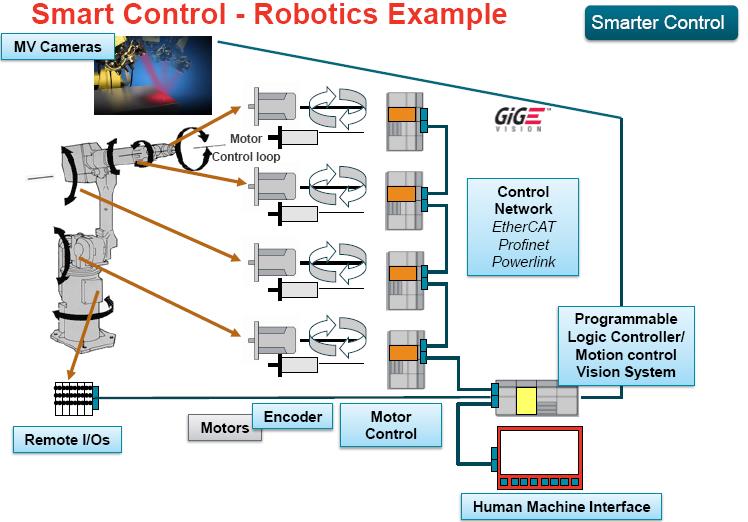

- FPGA的特点是擅长做信号的并行处理和硬件加速。Xilinx亚太区Zynq业务发展经理罗霖认为,在电机方面,由于现在中高端的机器人、数控机床等会用到六轴及以上的电机,这方面基本是FPGA一统天下。而三轴、四轴方案有时会看到x86、DSP和FPGA方案并存。

图1 机器人的智能控制示意图

中国现在四轴方案多一些,但是未来会向中高端去做。因为现在中国的电子元器件加工,食品饮料生产线、汽车生产线还主要靠采购国外设备,未来会逐渐国产化。

“针对工厂自动化设备、高端数控机床、机

- 关键字:

Xilinx FPGA

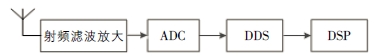

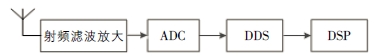

- 短波通信又称高频通信,是利用HF波段(3-30MHz)电磁波进行的无线电通信。短波通信主要靠天波传播,可经电离层一次或数次反射,最远可传至上万里,如按气候、电离层的电子密度和高度的日变化以及通信距离等因素选择合适频率,就可用较小功率进行远距离通信。短波通信设备较简单,机动性大,因此也适应于应急通信和抗灾通信。现代短波通信接收机正向着数字化、大通信带宽方向发展。文献[1-3]研究了短波通信的数字化实现方式,但其未对短波通信的大带宽应用进行探讨;文献[4-6]研究了通信信道化算法,其对一定带宽内的多信道高

- 关键字:

FPGA 接收机

- 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

具体实现

结构设计

基于抽取滤波器的工作原理,本文采用XC2V1000实现了一个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL共同完成源文件设 计。图1是抽取滤波器的顶层原理图。其中,clock是工作时钟,reset是

- 关键字:

FPGA FIR

- 本文叙述概括了FPGA应用设计中的要点,包括,时钟树、FSM、latch、逻辑仿真四个部分。

FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。早期的FPGA相对比较简单,所有的功能单元仅仅由管脚、内部buffer、LE、RAM构建而成,LE由LUT(查找表)和D触发器构成,RAM也往往容量非常小。现在的FPGA不仅包含以前的LE,RAM也更大更快更灵活,管教IOB也更加的复杂,支持的IO类型也更多,而且内部还集成了一些特殊功能单元,

- 关键字:

FPGA FSM 时钟树 仿真

- 进入电子,无处不用到按键, FPGA中的按键消抖动更是非同一般,并针对不同情况有相应的对策。

- 关键字:

FPGA MCU 按键消抖

- Xilinx亚太区销售及市场副总裁杨飞在2014岁末如此总结:以前FPGA厂商的目标是填补ASIC和ASSP空白,现在我们说取代ASIC、ASSP,而我们现在要做的就是,不仅是硬件,还有软件方面,让系统级的架构工程师和软件编程工程师也能够直接使用FPGA。 Xilinx亚太区销售及市场副总裁杨飞 因为FPGA到今天为止,从来不乏风险投资公司的介入,但是三十多年以来,初创企业总是做不成、长不大,根本原因和最大挑战不是说FPGA公司是硬件公司,因为我们根本是一家搞软件的公司。FPGA就是把硬件变成软件

- 关键字:

Xilinx FPGA NI

- Altera公司今天宣布,微软采用Altera Arria® 10 FPGA (现场可编程门阵列)实现基于CNN (卷积神经网络)算法的数据中心加速功能,其每瓦性能非常优异。这些算法通常用于图像分类、图像识别,以及自然语言处理等。

微软研究人员在云技术上不断取得进展,采用Arria 10开发套件和Arria 10 FPGA工程样片,展示了每瓦40 GFLOPS的性能——数据中心业界最好的性能水平。而且,与GPGPU相比,在CNN平台上,这一FPGA的性能功耗比是C

- 关键字:

Altera FPGA

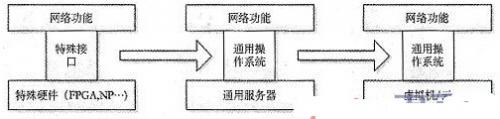

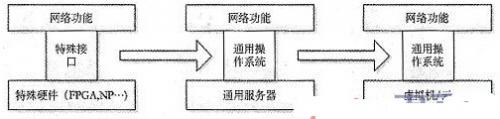

- 0概述

在传统的电信IT产品中,高性能网络接口一般采用特殊的硬件模块来实现,比如网络处理器、ASIC、FPGA等等。这些特殊硬件模块一般会采用特殊的架构和指令集对网络数据收发过程进行优化以达到更好的性能。然而,这也相应使得开发和维护这些模块的成本非常的昂贵,同时还有一个无法解决的问题是基于这些特殊硬件模块实现的网络接口不能移植到云中,因为它们跟硬件的耦合度太高了。摩尔定律的出现,使得通用处理器的性能得到了极大的提升,这也为基于通用处理器实现高性能网络接口提供了可能,同时也为移植到云中提供了前提条

- 关键字:

网络接口 FPGA

spartan.fpga介绍

您好,目前还没有人创建词条spartan.fpga!

欢迎您创建该词条,阐述对spartan.fpga的理解,并与今后在此搜索spartan.fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473