零基础学FPGA(十六)testbench很重要,前仿真全过程笔记(下篇)

—— 零基础学FPGA(十八)testbench很重要,前仿真全过程笔记(下篇)

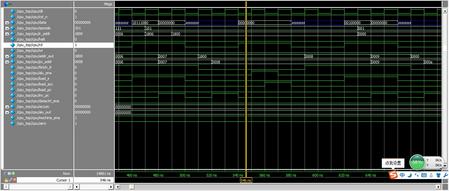

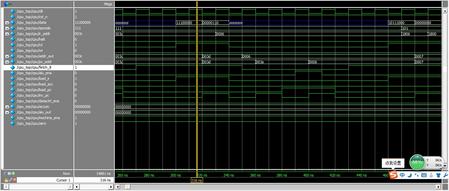

进入波形仿真后点击运行按钮即可出波形,下面我们来验证我们的cpu代码是否正确

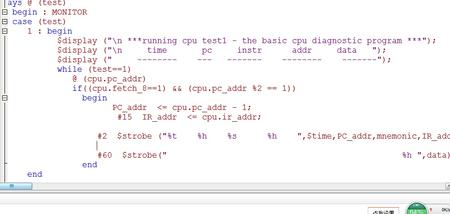

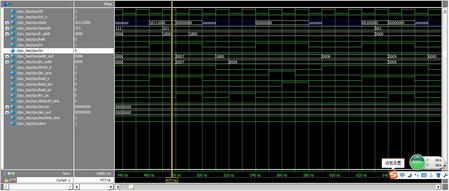

本文引用地址:https://www.eepw.com.cn/article/270619.htm大家先看两个图,等会小墨同学会结合这两个图给大家细细讲解仿真过程

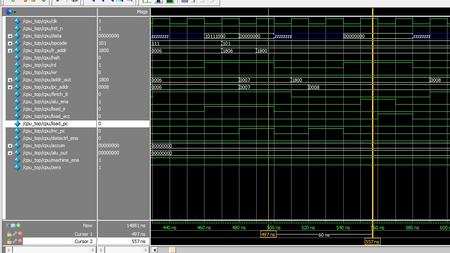

我们先来看第一个过程

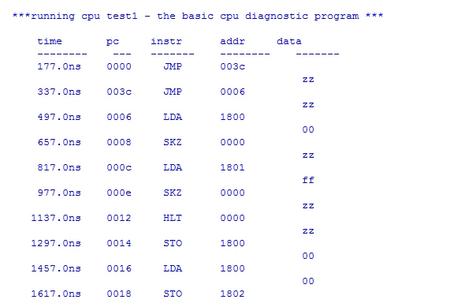

上电后,cpu先从ROM中读回两个周期的数据,是从ROM的0地址开始的,再对比我们之前定义好的ROM,数据读取正确,读回的数据的前三位是111,即指令码JMP,后13位003c为地址码,JMP指令是将读回的数据作为新的地址码来读取相应地址的数据。那么,下一步,cpu应该是从ROM的003c地址处读数据才对,再看一下波形

对比波形后可知,cpu正好是从003c处读取数据,读到的数据指令码位111即JMP,地址码位0006,再到ROM的0006地址处看

fpga相关文章:fpga是什么

低通滤波器相关文章:低通滤波器原理

评论