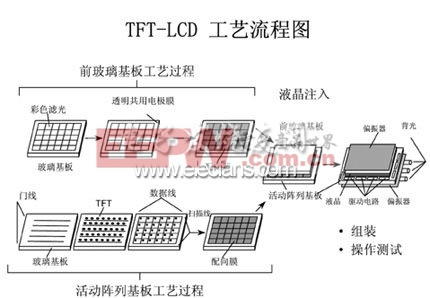

- 薄膜晶体管液晶显示器(TFT-LCD)通常采用两个加工过程并行进行加工成成品,如图1所示。其基本工艺如下: ● 通过前玻璃基板/彩色滤光基板工艺过程形成精确排列的彩色滤光层。 ● 薄膜基板工艺形成薄膜晶体

- 关键字:

工艺 技术 制造 TFT-LCD

- 印制电路制造者都希望选用性能良好的干膜,以保证印制板质量,稳定生产,提高效益。近年来随着电子工业的迅速发展,印制板的精度密度不断提高,为满足印制板生产的需要,不断有推出新的干膜产品,性能和质量有了很大

- 关键字:

干膜技术 工艺 性能

- 1 引言 锂电池产品以高能量密度、长循环寿命、快速充放电、高电池电压、工作温度范围广、无记忆等优异特性占据了市场很大份额。然而,锂电池产品在充放电过程中的过充电、过放电、放电过电流及其它异常状态(例如

- 关键字:

保护 电路设计 电池 聚合物 CMOS 工艺 基于

- 1、引言 倒装芯片的成功实现与使用包含诸多设计、工艺、设备与材料因素。只有对每一个因素都加以认真考虑和对待才能够促进工艺和技术的不断完善和进步,才能满足应用领域对倒装芯片技术产品不断增长的需要。 2

- 关键字:

技术应用 工艺 芯片 环境 SMT

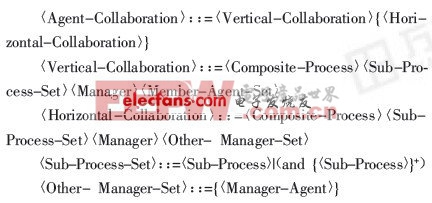

- 1 引言 敏捷制造是面向21世纪的企业发展战略和模式,虚拟企业(或企业动态联盟)是实现敏捷制造的主要途径。虚拟企业克服了传统企业的封闭性、局限性和设计、制造能力的不完备性,强调充分利用社会上已有的设计、制

- 关键字:

设计 系统 研究 工艺 虚拟 软件 Agent 基于

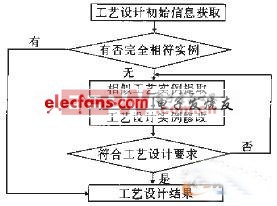

- 1 引言 作为连接设计和制造的桥梁和纽带,CAPP不仅是制造企业准备工作的首要步骤,而且是企业各部门信急交汇的重要环节。由于CAPP在CIMS中的地位和作用,工艺规划的自动生成(也即智能工艺设计)被视为生产自动化中

- 关键字:

设计 系统 工艺 智能 实例 基于

- 模具的型芯和型腔往往具有各种自由曲面,非常适合在数控机床上进行加工。数控加工的工艺与普通加工工艺有较大区别。本文结合儿童产品装饰物的模具型芯的数控加工工艺设计,分析和总结了模具数控加工的工艺特点,为模

- 关键字:

模具型芯 工艺 分析 数控加工

- 早期在小积体电路时代,每一个6吋的外延片上制作数以千计的芯片,现在次微米线宽的大型VLSI,每一个8吋的外...

- 关键字:

LED 外延片 工艺

- 摘要:为了提高运算放大器的驱动能力,依据现有CMOS集成电路生产线,介绍一款新型BiCMOS集成运算放大电路设计,探讨BiCMOS工艺的特点。在S-Edit中进行“BiCMOS运放设计”电路设计,并对其电路各个器件参数

- 关键字:

BiCMOS CMOS 工艺 放大器设计

- 近几年,在科技部、信息产业部等的大力引导下,半导体照明产业人气鼎盛,其中led封装业由于进入门槛相对较低,吸引...

- 关键字:

LED 封装 工艺

- 本文给出了一种低电压全差分套筒式运算放大器的设计方法,同时对该设计方法进行了仿真,从仿真结果可以看出,在保证高增益、低功耗的同时,该设计还可以满足20 MHz流水线模数转换器中运放的设计要求。

- 关键字:

mCMOS 0.6 工艺 全差分

- 随着大规模集成电路技术的发展与成熟,CMOS工艺以其低成本、低功耗、高集成度的优点使得采用CMOS工艺实现高性能集成锁相环具有十分重要的意义和广阔的前景。

- 关键字:

芯片 设计 相环 电荷 CMOS 工艺 基于

- 变压器绕组绕在磁芯骨架上,特别是饶组的层数较多时,不可避免的会产生分布电容,由于变压器工作在高频状态下,那么这些分布电容对变压器的工作状态将产生非常大的影响,如引起波形产生振荡,EMC变差,变压器发热等。

- 关键字:

变压器 电容 工艺 分布

- 随着半导体工艺开发和制造成本的快速上升和复杂程度不断加深,半导体制造商如今面临着前所未有的挑战。为了满足成本更低和功能更多的产品需求,半导体工艺的更新换代取决于不同器件类型的升级和集成——核

- 关键字:

TCAD 计算机辅助 工艺 设计技术

- 贾凡尼现象或贾凡尼效应是指两种金属由于存在电位差,通过介质产生了电流,继而产生了电化学反应,致使电位高的阳极被氧化的现象.本文中我们将各方面探讨分析PCB化学镀银工艺中贾凡尼现象存在的原因和处理方法。

- 关键字:

PCB 化学镀银 工艺 分析

sf4x 工艺介绍

您好,目前还没有人创建词条sf4x 工艺!

欢迎您创建该词条,阐述对sf4x 工艺的理解,并与今后在此搜索sf4x 工艺的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473