- 存储器共有13个寄存器,BANK0~BANK5只需要设置BWSCON和BANKCONx(x为0~5)两个寄存器;BANK6、BANK7外接SDRAM时,除了BWSCON和BANKCONx(x为6、7)外,还要设置REFRESH、BANKSIZE、MRSRB6、MRSRB7等4个寄存器。下面分类说明(“[y:x]”表示占据了寄存器的位x、x+1、……、y):

1. 位宽和等待控制寄存器BWSCON(Bus Width & Wait Sta

- 关键字:

ARM SDRAM

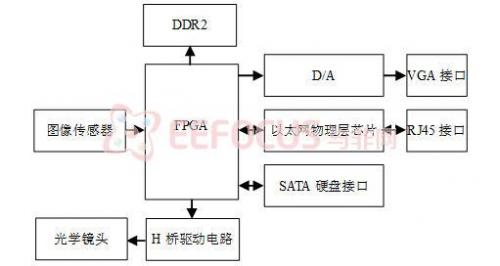

- 摘要:为了解决在一个屏幕上收看多个信号源的问题,对基于FPGA技术的视频图像画面分割器进行了研究。研究的主要特色在于构建了以FPGA为核心器件的视频画面分割的硬件平台,首先,将DVI视频信号,经视频解码芯片转换为

- 关键字:

FPGA DDR2 SDRAM 视频提取 图像合成

- 高速SDRAM存储器接口电路设计SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。一般比较常用的SDRAM

- 关键字:

SDRAM FPGA 最小系统 电路分析

- 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序操作,设计了DDR SDRAM 的数据与命令接口。用控

- 关键字:

SDRAM FPGA DDR 控制器

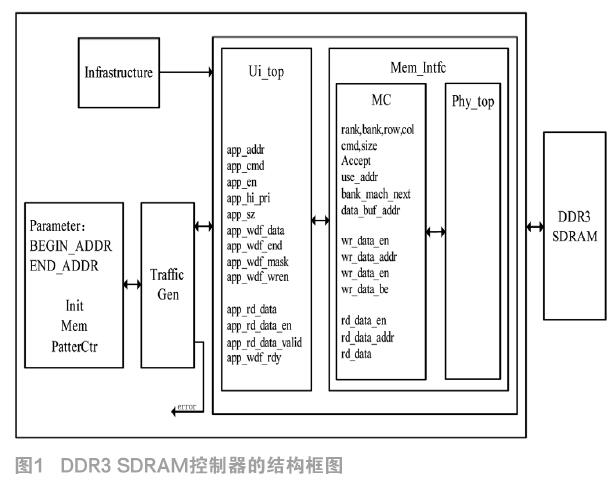

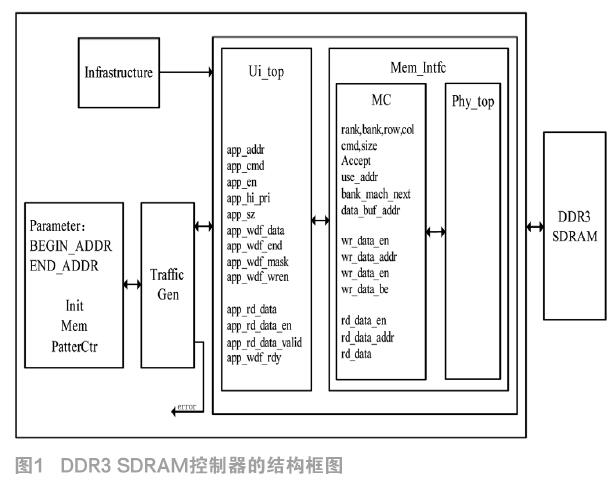

- DDR3 SDRAM内存的总线速率达到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作电压,采用90nm制程达到2Gbits的高密度。这个架构毫无疑问更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DI

- 关键字:

SDRAM FPGA DDR3 接口设计

- 今天我们来讲的是SDRAM的架构以及设计,这也是小墨第一次接触架构,也谈不上给大家讲,就是把我理解的当做一个笔记分享给大家,我也试着做了一个SDRAM 的架构word文档,在文章的后面,喜欢的朋友可以下载下来看一下

- 关键字:

SDRAM FPGA

- 高速电路设计领域,关于布线有一种几乎是公理的认识,即“等长”走线,认为走线只要等长就一定满足时序需求,就不会存在时序问题。本文对常用高速器件的互连时序建立模型,并给出一般性的时序分析公式。为

- 关键字:

PCB DDR SDRAM PHY芯片

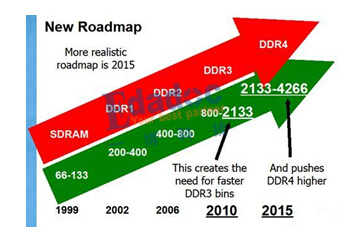

- DRAM (动态随机访问存储器)对设计人员特别具有吸引力,因为它提供了广泛的性能,用于各种计算机和嵌入式系统的存储系统设计中。本文概括阐述了DRAM 的概念,及介绍了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DD

- 关键字:

存储器 DRAM SDRAM

- SDRAM与DDR SDRAM

SDRAM是比较久远的事情了,但我们一说到它肯定不会和 DDR混淆,我们通常理解的SDRAM其实是SDR SDRAM,为SDRAM的第一代,而DDR1则为第二代,乃至到我们现在使用的DDR4,其实为第五代SDRAM,在此需要澄清一下。以示区别,后续文 章里面用SDR来特指SDR SDRAM,而DDR就特指DDR SDRAM了。

就像很多人回复的一样,他们的本质区别就是周期操作方 式(也称时钟采样)的差异,这就导致后面设计上很大的不同。SDR都是“

- 关键字:

DDR SDRAM

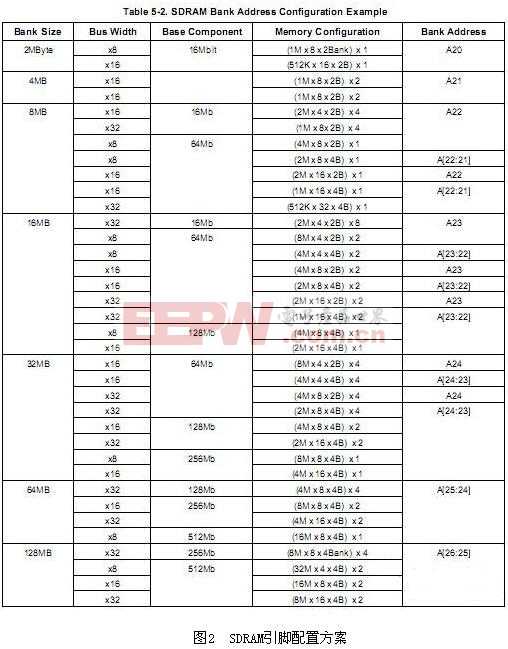

- 介绍SDRAM电路设计之前先了解下SDRAM的寻址原理。SDRAM内部是一个存储阵列,可以把它想象成一个表格,和表格的检索原理一样,先指定行,再指定列,

- 关键字:

SDRAM 电路设计

- RAMRAM是指通过指令可以随机的、个别的对各个存储单元进行访问的存储器,一般访问时间基本固定,而与存储单元地址无关。RAM的速度比较快,但其保

- 关键字:

SRAM DRAM SDRAM 比较

- 为了使DDR3 SDRAM更方便、多样地用于工程开发中,本文对XILINX公司DDR3 SDRAM提供的MIG核进行了分析研究,并在此基础上实现了大容量数据缓冲区的逻辑设计。通过对系统中各模块的作用及相互间关系的研究,发现该控制器256位接口对工程开发十分不便,通过创建FIFO控制系统和读写接口FIFO的方式,将接口转换为64位。该方案对控制核重新构建并上板测试,均符合高速数据传输缓存的要求,使DDR3成为一个大容量且可控的高速FIFO。

- 关键字:

MIG核 FIFO DDR3 SDRAM 201608

- 特权同学对存储器的认识也许还很肤浅,但是不要紧,学习靠积累,靠总结。希望在大话存储器的一些文章里总结归纳一些和存储器相关的知识,也希望能够理出一条清晰的思路,让大家也让我自己对存储器有更深入的认识何了解。

提到存储器相信没有人会陌生,也许你的第一反应会是PC机的内存条、硬盘,如果你是个电子行业的学生或者从业者,你也许还会想到FLASH、SRAM、SDRAM、EEPROM等等。的确,信息时代的存储器可谓无处不在,也正是因为有了存储器,才让计算机(特权同学认为这个计算机的概念不仅仅是电脑,嵌入式的任

- 关键字:

存储器 SDRAM

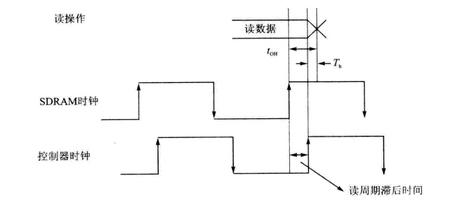

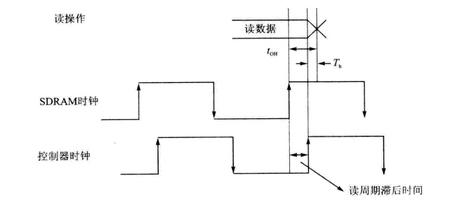

- 七、SDRAM工作时钟相位偏移计算

从上篇文章中我们知道,我们的数据是要经过一定的延时才会到达目标器件的,这个延时也就是相对于源寄存器的时钟发射沿的时间延时,数据在源寄存器时钟的上升沿到来时输出,经过FPGA的走线,PCB走线等,到达目标寄存器的数据端口时会有一定的延时,而这个数据要想被目标器件的目的寄存器锁存,那么,目的寄存器的锁存时钟应该尽量在数据的有效窗口内才能确保数据被捕获成功。所谓数据的有效窗口,就是数据在两次变化之间的中间部分,也是数据最稳定的部分。

所以,要想将数据正确捕获,

- 关键字:

FPGA SDRAM

- 下面我们进入正题,今天我们讲时序

一、从静态时序分析说起

我理解的静态时序分析,就是我们在不加激励的情况下,通过对电路进行时序的延迟计算,预计电路的工作流程,对电路提出我们需要的一些约束条件,比如我们需要从A寄存器到B寄存器的延迟不能大于10ns,如果我们不添加时序约束,综合工具可能会有好几条路径,按照它自己的要求来布局布线,那么从A寄存器到B寄存器的时间就有可能是20ns或者15ns之类的路径,而我们需要的是不能大于10ns,因此,我们需要添加时序约束,再根据特定的时序模型,使我们的系统

- 关键字:

FPGA SDRAM

sdram介绍

SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

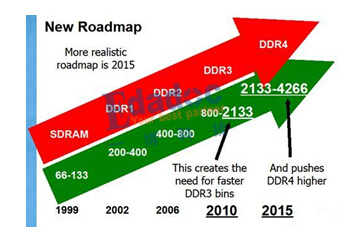

SDRAM从发展到现在已经经历了四代,分别是:第一代SDR SDRAM,第二代DDR [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473