- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握步进电机技术与实现方法;(3)学习用Verilog HDL行为描述方法描述步进电机。实验任务本实验的任务设计一个步进电机运行控制电路,A、B、C、D分别表示步进电机的四相绕组,步进电机按四相四拍的方式运行。如要求电机正传时,控制端T=1,电机的四相绕组的通电顺序为AC—DA—BD—CB—AC……如要求电机反传时,控制端T=0,电机的四相绕组的通电顺序为AC—CB—BD—DA—AC……。实验原理为了

- 关键字:

步进电机 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握步进电机的原理和设计方法;(3)学习用Verilog HDL描述一个步进电机电路。实验任务本实验的任务是设计控制四相绕组的步进电机电机正转、反转、停止的控制电路。要求如下:电机运转规律为:正转30s→停10s→反转30s→停10s→正转30s……实验原理步进电机是将电脉冲信号转变为角位移或线位移的开环控制元步进电机件。当电流流过定子绕组时,定子绕组产生一矢量磁场。该磁场会带动转子旋转一角度,使得转

- 关键字:

步进电机 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握计数器原理;(3)掌握用Verilog HDL数据流和行为级描述寄存器单元的方法。实验任务设计简单秒表(60进制),并要求带启动、复位、暂停功能。实验原理如下所示,秒表(60进制)即显示从00到59循环跳转计数。并且通过开关设置,达到复位至00,任意时刻暂停和启动的功能。我们通过将开发板的12M晶振分频(参考分频程序)出1Hz的计时频率,实现秒钟的效果。将clk_1s的上升沿作为触发信号计时。通过

- 关键字:

秒表计数器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握分频器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务设计一个任意整数分频器。实验原理时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频

- 关键字:

分频器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握扭环形计数器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务设计一个右移扭环形计数器。实验原理将移位寄存器的输出非q0连接到触发器q3的输入,这样就构成了一个扭环形计数器。初始化复位时,给q0一个初值0000,则在循环过程中依次为:000010001100111011110111001100010000。Verilog HDL建模描述用行为级描述右移扭环形计数器程序清单tw

- 关键字:

扭环形计数器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握环形计数器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务设计一个4位右循环一个1的环形计数器。实验原理将移位寄存器的输出q0连接到触发器q3的输入,并且在这4个触发器中只有一个输出为1,另外3个为0,这样就构成了一个环形计数器。初始化复位时,给q0一个置位信号,则唯一的1将在环形计数器中循环移位,每4个时钟同期输出一个高电平脉冲。Verilog HDL建模描述用行为级描述

- 关键字:

环形计数器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握移位寄存器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务本实验的任务是设计一个7位右移并行输入、串行输出的移位寄存器。实验原理如果将多个触发器级联就构成一个多位的移位寄存器,如下图所示,是以4位移位寄存器为例的逻辑电路图,其中的LD/SHIFT是一个置数/移位控制信号。当LD/SHIFT为1时,在CP作用下,从输入端A、B、C、D并行接收数据;当LD/SHIFT为0时,在

- 关键字:

移位寄存器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握JK触发器原理;(3)学习用Verilog HDL语言行为机描述方法描述JK触发器电路。实验任务本实验的任务是设计一个JK触发器实验原理带使能端RS锁存器的输入端R=S=1时,锁存器的次态不确定,这一因素限制了其应用。为了解决这个问题,根据双稳态元件两个输出端互补的特点,用Q和非Q反馈控制输入信号,并用J代替S,用K代替R,构成了J-K锁存器。Verilog HDL建模描述用行为级描述实现的带异步

- 关键字:

JK触发器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握D触发器原理;(3)学习用Verilog HDL语言行为机描述方法描述D触发器电路。实验任务本实验的任务是描述一个带有边沿触发的同步D触发器电路,并通过STEP FPGA开发板的12MHz晶振作为触发器时钟信号clk,拨码开关的状态作为触发器输入信号d,触发器的输出信号q和~q,用来分别驱动开发板上的LED,在clk上升沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。实验原理从D触发器的特

- 关键字:

D触发器 FPGA Lattice Diamond Verilog HDL

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握RS触发器原理;(3)学习用Verilog HDL语言行为级描述方法描述RS触发器电路。实验任务本实验的任务是描述一个RS触发器电路,并通过STEP FPGA开发板的12MHz晶振作为触发器时钟信号clk,拨码开关的状态作为触发器输入信号S,R,触发器的输出信号Q和非Q,用来分别驱动开发板上的LED,在clk上升沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。实验原理基本RS触发器可以由两

- 关键字:

RS触发器 FPGA Lattice Diamond Verilog HDL

- 1. 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握数码管驱动;(3)学习用Verilog HDL描述数码管驱动电路。2. 实验任务在数码管上显示数字。3. 实验原理数码管是工程设计中使用很广的一种显示输出器件。一个7段数码管(如果包括右下的小点可以认为是8段)分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成。实际是由8个LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如下图

- 关键字:

七段数码管 FPGA Lattice Diamond Verilog HDL

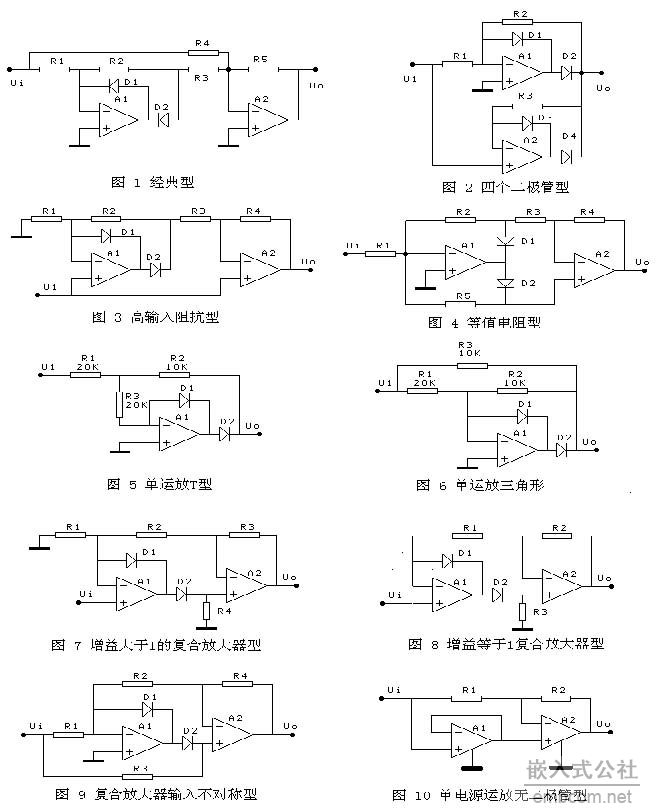

- MOS管因为其导通内阻低,开关速度快,因此被广泛应用在开关电源上。而用好一个MOS管,其驱动电路的设计就很关键。下面分享几种常用的驱动电路。电源IC直接驱动电源IC直接驱动是最简单的驱动方式,应该注意几个参数以及这些参数的影响。· 查看电源IC手册的最大驱动峰值电流,因为不同芯片,驱动能力很多时候是不一样的。· 了解MOS管的寄生电容,如图C1、C2的值,这个寄生电容越小越好。如果C1、C2的值比较大,MOS管导通的需要的能量就比较大,如果电源IC没有比较大的驱动峰值电流,那么管子导通的速度就比较慢,就达

- 关键字:

MOS管 驱动 电路 设计

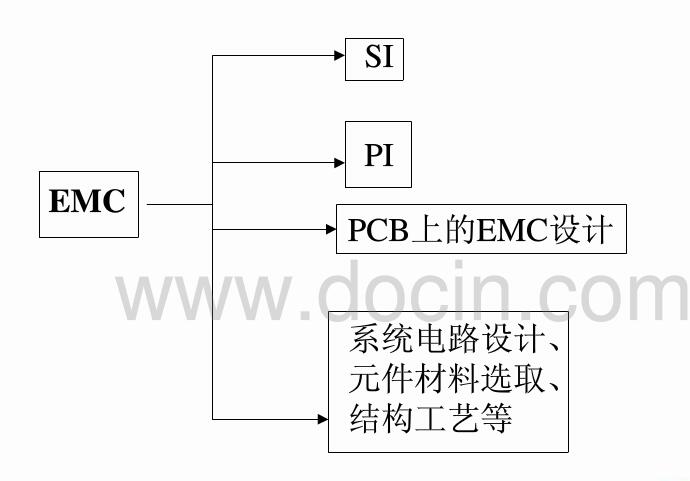

- 关于MOS管驱动电路设计,本文谈一谈如何让MOS管快速开启和关闭。一般认为MOSFET(MOS管)是电压驱动的,不需要驱动电流。然而,在MOS管的G极和S极之间有结电容存在,这个电容会让驱动MOS变的不那么简单。下图的3个电容为MOS管的结电容,电感为电路走线的寄生电感:如果不考虑纹波、EMI和冲击电流等要求的话,MOS管开关速度越快越好。因为开关时间越短,开关损耗越小,而在开关电源中开关损耗占总损耗的很大一部分,因此MOS管驱动电路的好坏直接决定了电源的效率。怎么做到MOS管的快速开启和关闭呢?对于一个

- 关键字:

MOS管 驱动电路 设计

- IT之家 3 月 13 日消息,据台媒中央社报道,半导体产业景气反转向下,晶圆代工产能松动,IC 设计厂为强化供应链,同时因未来可能变化的需求,纷纷针对货源展开多元布局,晶圆代工报价恐将面临压力。台媒指出,晶圆代工厂今年来因为终端市场需求疲弱,供应链持续调整库存,产能明显松动,世界先进第一季度产能利用率恐较去年第四季度下滑 10 个百分点,力积电将降至 6 成多水准,联电第一季度产能利用率也将降至 7 成。IC 设计厂多数表示,晶圆代工厂并未调降代工价格,不过厂商针对配合预先投片备货的客户提供优

- 关键字:

晶圆代工 IC 设计

- 摘要:针对目前电动汽车V2G充电桩单接口的充放电功率恒定、无法扩展的问题,设计一种双回路双接口的

V2G充放电系统,采用在功率模块直流侧进行功率投切控制的方式,使得充放电系统突破单接口额定功率的限

制,有效进行充放电功率扩展。样机的实验数据表明,充放电系统能够根据后台指令,控制相应的接触器投切

动作,完成回路间功率模块调用,准确响应后台功率需求,输出扩展后的充放电功率。关键词:V2G;充电桩;功率;扩展;设计0 引言我国新能源电动汽车保有量日益增多,作为“新基

建”之一的充电桩是连接电动汽车和电网

- 关键字:

202208 V2G 充电桩 功率 扩展 设计

hdl)设计介绍

您好,目前还没有人创建词条hdl)设计!

欢迎您创建该词条,阐述对hdl)设计的理解,并与今后在此搜索hdl)设计的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473