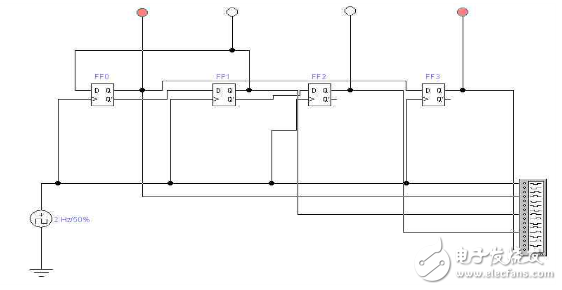

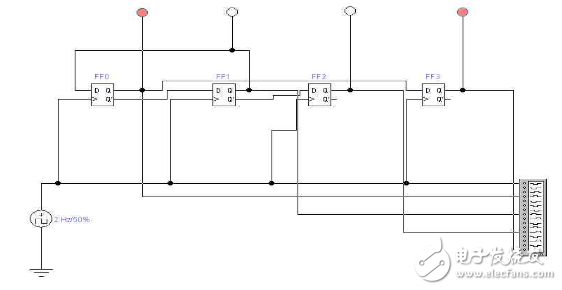

- 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握环形计数器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务设计一个4位右循环一个1的环形计数器。实验原理将移位寄存器的输出q0连接到触发器q3的输入,并且在这4个触发器中只有一个输出为1,另外3个为0,这样就构成了一个环形计数器。初始化复位时,给q0一个置位信号,则唯一的1将在环形计数器中循环移位,每4个时钟同期输出一个高电平脉冲。Verilog HDL建模描述用行为级描述

- 关键字:

环形计数器 FPGA Lattice Diamond Verilog HDL

- 基于探索仿真三态门总线传输电路的目的,采用Multisim10仿真软件对总线连接的三态门分时轮流工作时的波形进行了仿真实验测试,给出了仿真实验方案,即用Multisim仿真软件构成环形计数器产生各个三态门的控制信号、用脉冲信号源产生各个三态门不同输入数据信号,用Multisim仿真软件中的逻辑分析仪多踪同步显示各个三态门的控制信号、数据输入信号及总线输出信号波形,结论是仿真实验可直观形象地描述三态门总线传输电路的工作特性,所述方法的创新点是解决了三态门的工作波形无法用电子实验仪器进行分析验证的问题。

- 关键字:

三态门 总线传输 环形计数器 逻辑分析仪

环形计数器介绍

您好,目前还没有人创建词条环形计数器!

欢迎您创建该词条,阐述对环形计数器的理解,并与今后在此搜索环形计数器的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473