- 本次中国电子和中国电科在FPGA上取得的成绩,则充分说明了,自主研发的路是完全能够走通的。

- 关键字:

FPGA 相控阵雷达

- 我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。本公众号作者ALIFPGA,多年FPGA开发经验,所有文章皆为多年学习和工作经验之总结。 逻辑写多了,有时候一些基本的错误忘了避免了。 昨天设计逻辑的时候就不小心触雷了,有个信号有激励没响应,后来看了时序报告,有这么一句话。

&nbs

- 关键字:

FPGA

- 基于软件的图像处理方法存在着一些局限性,尤其是计算速度和算法效率方面。所以大家很自然的就想到了FPGA作为嵌入式图像应用的平台。许多图像处理本身就是并行计算的,并且FPGA的编程硬件,本质上也是并行的。但是利用FPGA硬件进行图像处理存在很多的困难,需要学到很多的技巧。下面我介绍两几种比较基础的图像处理算法思想。 单幅图像的点操作是图像处理中最简单的操作,输出值只取决于输入值,与位置无关,可以看作是一个函数的映射。从硬件实现的角度来说,最简单的方式就是通过一个实现函数的模块对输入的每个像素进行依次处

- 关键字:

FPGA 图像处理

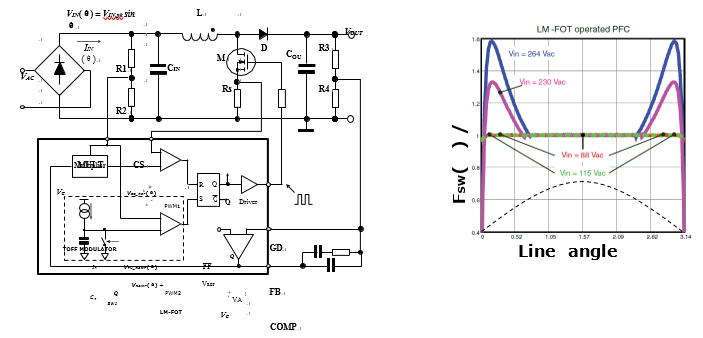

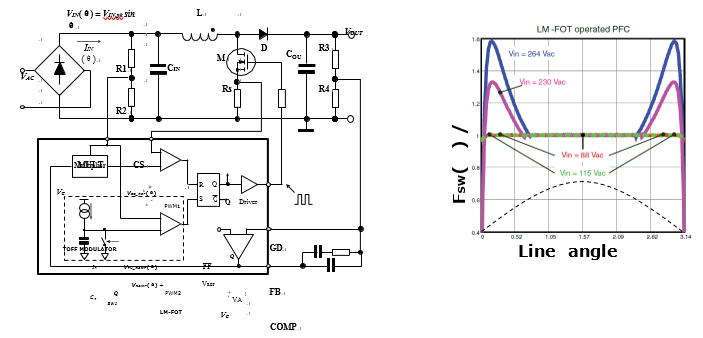

- 摘要 本文介绍一种创新的自适应稳压器(AC/DC或DC/DC)脉宽调制器(PWM) ,基于“固定关断时间(FOT)”或“恒定导通时间(COT)”控制方法,可以在全工况下(例如,满负载CCM或中低负载DCM模式,宽输入输出电压) 以恒定开关频率工作,无转换器的寄生参数(例如,功率开关和滤波电感器的电阻)的负面影响。此外,本文提出的调制器电路与转换器拓扑无关(升压、降压、反激式等),只与功率开关管栅极驱动逻辑信号(GD)有关,节省芯片引脚数量,且/或降低设计复杂程度。 前言 在一

- 关键字:

PWM 自适应

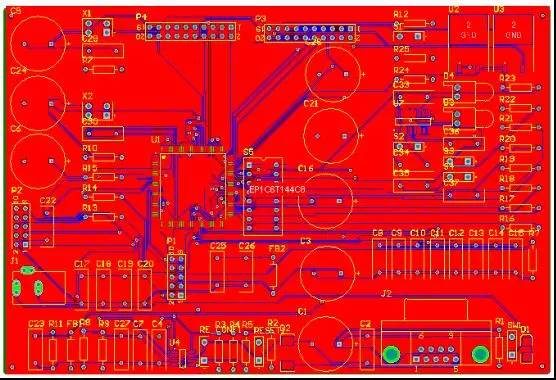

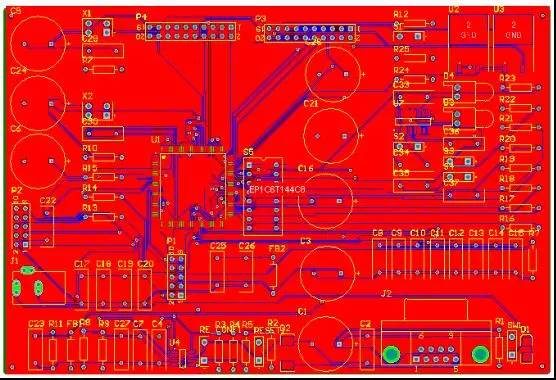

- 画FPGA开发板所犯的那些错误,小编这里先截下我最初画这个开发板的一张“惨不忍睹”的PCB让大家看看。 Top Layer如图:

Bottom Layer如图:

第一遍画的时候,想“速战速决”把它画完,草草了事,但是等全部布线完以后却发现这里面的错误实在是太多了,我觉得最核心的错误就是一开始就没有注意整个系统各个元器件的布局,从而导致了“灾难”的发生,后来的布线也就非常困难。大家很容易可以

- 关键字:

FPGA Layer

- 基于现场可编程门阵列(FPGA)的硬件加速器器件及嵌入式FPGA(eFPGA)领域内领导性企业Achronix半导体公司(Achronix Semiconductor Corporation)日前宣布:与专注于为电子系统设计人员提供半导体IP的半导体知识产权公司CAST Incorporated达成合作;CAST的高性能无损压缩IP已经被植入,以支持Achronix 的FPGA产品组合,用来完成数据中心和移动边缘间数据传输的高效处理。 CAST为Deflate

- 关键字:

CAST FPGA

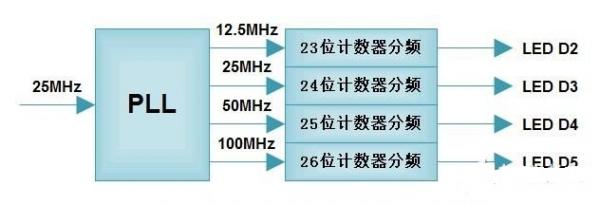

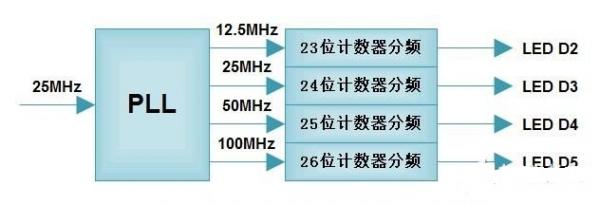

- 如图8.17所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100MHz的时钟信号,这4路时钟信号又分别驱动4个不同位宽的计数器不停的计数工作,这些计数器的最高位最终输出用于控制4个不同的LED亮灭。由于这4个时钟频率都有一定的倍数关系,所以我们也很容易通过调整合理的计数器位宽,达到4个LED闪烁一致的控制。

cy4.v模块代码解析 先来看cy4.v模块的

- 关键字:

FPGA PLL

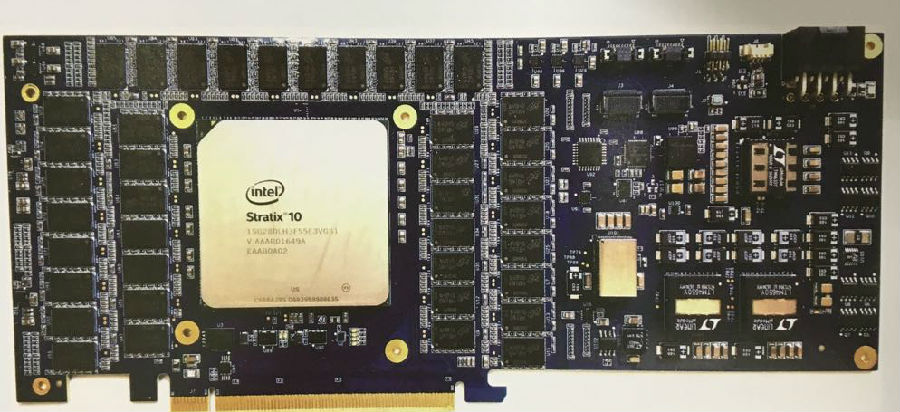

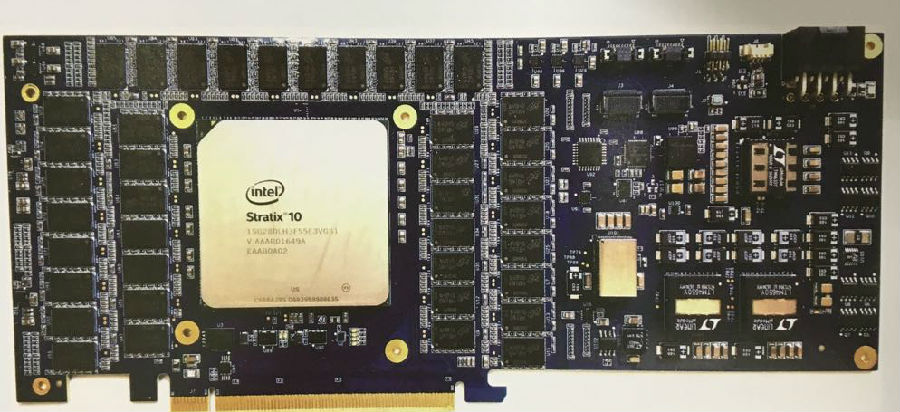

- “英特尔现在的定位是以数据为中心的企业,而过去是PC平台。”英特尔可编程解决方案事业部亚太区市场拓展经理刘斌先生称。他是在近日举行的“英特尔可编程解决方案新闻发布会”上说此番话的。

此次发布会主要介绍了三个内容:

*采用英特尔PAC(可编程加速卡)的戴尔服务器现已大量上市;此外,富士通也在支持重点客户使用。

*通过免费的PAC加速堆栈,可在常见软件开发环境中提供通用硬件加速性能。

*两个应用案例:面向财务风险分析和数据库加速的

- 关键字:

FPGA 英特尔

- 人工智能(AI)和大数据的不断发展带来对超高计算力的需求,使得相应硬件组成和算法架构也在不断创新中寻求突破,以达到新应用所需的计算能力。

- 关键字:

FPGA,加速,AI,大数据

- 人工智能(Artificial Intelligence, AI)无疑是近一两年来科技产业内最热门的话题,除了科技业巨头无不大力投入之外,金融等服务业者对导入人工智能,也展现出强烈兴趣。制造业对AI技术的关注,也不在话下,并且在相关关键技术逐渐到位的情况下,已开始有实际导入动作。 倡导智能制造不遗余力的研华科技,除了为各行各业提供对应的先进解决方案外,在自家生产在线也开始逐步导入人工智能要素。比如机台设备的状态侦测/诊断、原物料/能源的使用状况,乃至产品的品管流程等,均已逐步导入

- 关键字:

Arm FPGA

- 人工智能 (AI) 正在革新各行各业,改变数据的管理和解释方式,而且将帮助人们和企业更快地解决实际难题。 今天的 微软必应智能搜索(Intelligent Search)*新闻展示了英特尔® FPGA(现场可编程门阵列)技术正如何有效支持全球最先进的一些人工智能平台。借助实时人工智能,必应 (Bing)搜索引擎不仅能够提供标准搜索结果,还能满足用户的更多需求,帮助其快速了解所需知识和信息。必应智能搜索将提供答案而非网页,支持系统理解词语和词

- 关键字:

英特尔 FPGA

- 计算机发展到今天,已经大大改变了我们的生活,我们已经进入了智能化的时代。但要是想实现影视作品中那样充分互动的人工智能与人机互动系统,就不得不提到深度学习。 深度学习 深度学习的概念源于人工神经网络的研究。含多隐层的多层感知器就是一种深度学习结构。深度学习通过组合低层特征形成更加抽象的高层表示属性类别或特征,以发现数据的分布式特征表示。 深度学习的概念由Hinton等人于2006年提出。基于深信度网(DBN)提出非监督贪心逐层训练算法,为解决深层结构相关的优化难题带来希望,随后提出多层自动编码器深

- 关键字:

GPU FPGA

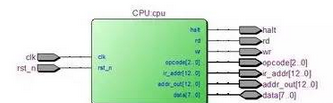

- CPU的主频高达几个GHz,FPGA的速率往往在几百兆。但是,往往我们会说FPGA会给CPU进行加速。 虽然CPU主频很高,但其是通用处理器,做某个特定运算(如信号处理,图像处理)可能需要很多个时钟周期;而FPGA可以通过编程重组电路,直接生成专用电路,加上电路并行性,可能做这个特定运算只需要一个时钟周期。 假设我们用FPGA完整的实现了CPU,然后再跑软件的话,的确比CPU慢。问题是FPGA不会那么干,它会直指问题本质,解决问题。

即使我们用FPGA实现一个CP

- 关键字:

FPGA CPU

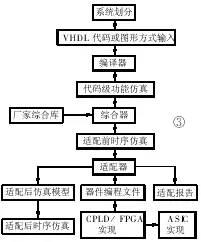

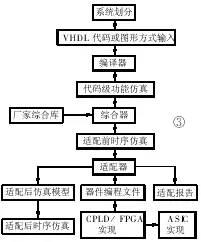

- FPGA是可编程芯片,因此FPGA的设计方法包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、存储器、输入输出接口电路以及其他设备,软件即是相应的HDL程序以及最新才流行的嵌入式C程序。硬件设计是基础,但其方法比较固定,本书将在第4节对其进行详细介绍,本节主要介绍软件的设计方法。 目前微电子技术已经发展到SOC阶段,即集成系统(Integrated System)阶段,相对于集成电路(IC)的设计思想有着革命性的变化。SOC是一个复杂的系统,它将一个完整产品的功能集成在一个芯片上,包

- 关键字:

FPGA

- 最近的几篇论文都改好投出去了,希望后面有好的结果。暂时也就有点闲暇时间空出来了,好久没有写技术文章来总结提炼一下了,今天难得就写一点。 每年到了找工作的时节,总会有很多迷茫的小本甚至是小硕在到处讯问说:我是不是应该去参加个培训班,去学一门什么什么技术。然后学哪个比较好找工作一点,学哪个收入会高一点等等。每当这个时候就有很多抱着就业目的的人来问到底学什么技术好啊,哪个技术有前途啊,等等。 一般在这个时候,我是不推荐这帮人去学习FPGA的。当然,并不是FPGA技术不好,也不是学FPGA技术没有前途,而

- 关键字:

FPGA SoC

fpga-pwm介绍

您好,目前还没有人创建词条fpga-pwm!

欢迎您创建该词条,阐述对fpga-pwm的理解,并与今后在此搜索fpga-pwm的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473