- Altera公司和IBM今天发布了业界第一款基于FPGA的加速平台,通过IBM的一致性加速器处理器接口(CAPI),实现FPGA与POWER8 CPU顺畅的连接。这一可重新配置的硬件加速器在FPGA和处理器之间有共享虚拟存储器,显著提高了高性能计算(HPC)和数据中心应用的系统性能、效率和灵活性。在超级计算2014年度大会上,Altera和IBM展示的几种POWER8系统能够使用FPGA实现连续加速。

通过与OpenPOWER基金会一起工作,Altera和IBM开发了非常灵活的异构计算解决方案,

- 关键字:

Altera IBM FPGA

- Analog Devices, Inc. (ADI: NASDAQ) 最近推出一款快速原型制作套件,其可简化宽动态范围 GSPA 数据转换器到 FPGA(现场可编程门阵列)的连接。 数字和模拟设计人员可以采用快速原型制作套件 AD-FMCDAQ2-EBZ ,在主要的 FPGA 平台(包括 Xilinx 的 UltraScale FPGA,以及 Zynq 用于雷达、仪器仪表、无线电和其它数据采集应用的所有可编程 SoC 器件)上快速地对高速 JEDEC JESD204B SerDes(串行器/解串器)G

- 关键字:

ADI FPGA SoC

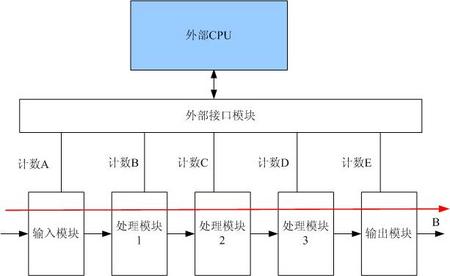

- 如果设计中有多个模块,每个模块内部有许多寄存器或者存储块需要配置或者提供读出那么实现方式有多种,主要如下:

实现方式一:可以在模块顶部将所有寄存器引出,提供统一的模块进行配置和读出。这种方式简单是简单,但是顶层连接工作量较大,并且如果配置个数较多,导致顶层中寄存器的数目也会较多。

实现方式二:通过总线进行连接,为每个模块分配一个地址范围。这样寄存器等扩展就可以在模块内部进行扩展,而不用再顶层进行过多的顶层互联。如下图所示:

那如果进行总线的选择,那么有一种

- 关键字:

FPGA AVALON

- 有个笑话说,有个病人感冒了,于是去看医生,医生诊断后说,你得了感冒,但是我只会治疗肺炎,不如你回家再浇点凉水,把病恶化成肺炎,那我能治了。这个笑话展示了庸医误人。但是另一方面,从逻辑上来讲,医生则是一个把未知问题转化成已知问题的高手。

不说笑话,下面出两个题目,其分别是

问题1:运用数字电路,如何将一个时钟域的上升沿,转换成另一个时钟域的脉冲信号(单周期信号)。

问题2:运用数字电路,如何将一个时钟域的脉冲信号(单周期信号),转换成另一个时钟域的上升沿。

可能乍一看,这两个题目

- 关键字:

FPGA 数字电路

- 当下,最火的学问莫过于《大数据》,大数据的核心思想就是通过科学统计,实现对于社会、企业、个人的看似无规律可循的行为进行更深入和直观的了解。FPGA的可测性也可以对FPGA内部“小数据”的统计查询,来实现对FPGA内部BUG的探查。

可测性设计对于FPGA设计来说,并不是什么高神莫测的学问。FPGA的可测性设计的目的在设计一开始,就考虑后续问题调试,问题定位等问题。要了解FPGA可测性设计,只不过要回答几个问题,那就是:

(1) 设计完成如何进行测试?

(2)

- 关键字:

FPGA JTAG

- 作为FPGA工程师来说,碰到新的问题是设计中最常见的事情了,技术发展趋势日新月异,所以经常会有新的概念,新的需求,新的设计等待去实现。不是每个通过BAIDU或者GOOGLE都有答案。

因此,新的设计经常会有,那如何实现?

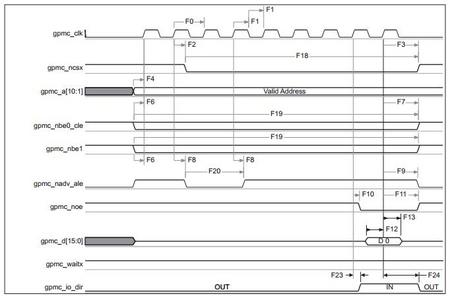

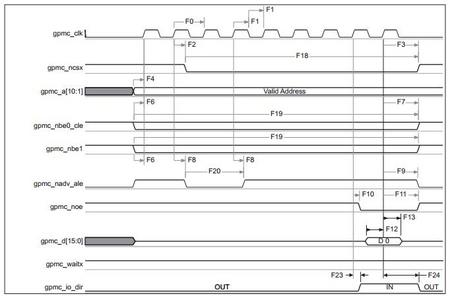

假设,FPGA需要设计一个接口模块,那我们就需要了解一下几个问题:

(1) 同步接口还是异步接口模块;

(2) 有哪些信号,功能是什么?

(3) 信号之间时序关系是什么?

(4) 传递的效率能够达到多少;

(5) 等等!

谁会给予这些答

- 关键字:

FPGA 测试 接口

- 写在coding之前的那些铁律

(1)注释: 好的代码首先必须要有注释,注释至少包括文件注释,端口注释,功能语句注释。

文件注释:文件注释就是一个说明文:这通常在文件的头部注释,用于描述代码为那个工程中,由谁写的,日期是多少,功能描述,有哪些子功能,及版本修改的标示。这样不论是谁,一目了然。即使不写文档,也能知道大概。

接口描述:module的接口信号中,接口注释描述模块外部接口,例如AHB接口,和SRAM接口等等。这样读代码的人即可能够判断即模块将AHB接口信号线转换成SRAM接口

- 关键字:

FPGA coding 时序

- 1 项目背景

1.1 研究背景

LCD显示屏的应用越来越广,数量越来越多。LCD显示屏应用广泛,无处不在。小到家庭各种电器设备,大到军事设备。更常见是用于各种公共场合如体育馆、广场等商业用途。给我们传递一种更为直观、生动的信息。从此我们的生活发生了巨大改变。巨大的应用巨大的市场带来了巨大的商机。传统的显示器大多采用控制系统与显示界面集成在一起的方案,不便于实时管理与有效维护,不便于及时更新;也不便于人亲临恶劣的工作环境下进行人为操控。LED显示屏用户迫切需要实现对LED显示屏的远程控制。

- 关键字:

FPGA LCD Microblaze

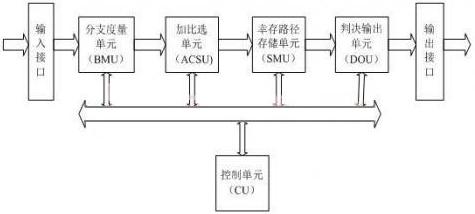

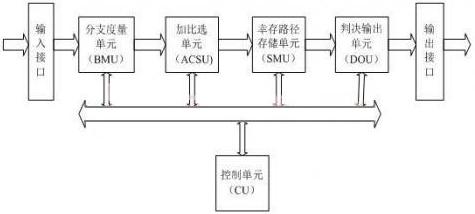

- 卷积码是广泛应用于卫星通信、无线通信等各种通信系统的信道编码方式。Viterbi算法是一种最大似然译码算法。在码的约束度较小时,它比其它概率译码算法效率更高、速度更快,译码器的硬件结构比较简单。随着可编程逻辑技术的不断发展,其高密度、低功耗、使用灵活、设计快速、成本低廉、现场可编程和反复可编程等特性,使FPGA逐步成为Viterbi译码器设计的最佳方法。项目目的是用FPGA实现一个Viterbi译码器。

一、译码器功能分析

译码器是一种具有“翻译”功能的逻辑电路,这

- 关键字:

FPGA Viterbi 译码器

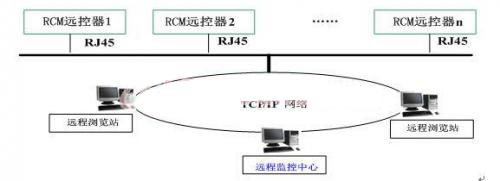

- 项目研究的目的和主要研究内容

研究目的

为了远程对现场进行设备管理和环境监控,并简化现场监控设备,有效地提高整个系统的稳定性和安全性。拟开发一款远程控制器,简称RCM远控器。该远控器将集现场数据采集、多种通信协议转换、故障告警、应急控制、智能联动、内嵌WEB配置页等多项功能。

主要研究内容

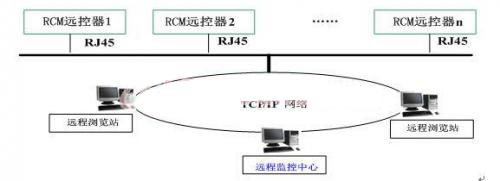

1.远程监控系统

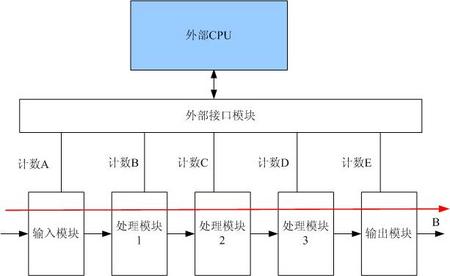

远程监控系统总体结构(如图1所示),其中主要研究内容为RCM远控器。

图 1

远控器通过RJ45与TCP/IP网络开放式网络相

- 关键字:

FPGA DSP RCM

- 1设计摘要

1.1项目背景

汉字作为非字母化、非拼音化的文字,在当今高度信息化的社会里,如何快速高效地将汉字输入计算机,已成为影响人机交流信息效率的一个重要瓶颈。目前,汉字输入主要分为人工键盘输入和机器自动识别输入两种,其中人工键入速度慢且劳动强度大。自动识别输入分为语音识别和汉字识别两种,其中汉字识别是将汉字点阵图形转换成电信号,然后输入给数字信号处理器或计算机进行处理,依据一定的分类算法在汉字字符集合中识别出与之相匹配的汉字。因此,研究脱机手写体汉字识别的目的就是解决汉字信息如何高速输

- 关键字:

FPGA 神经网络 汉字识别

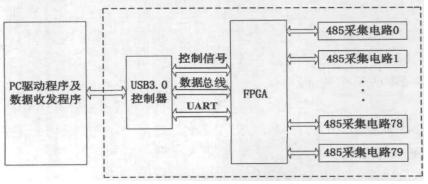

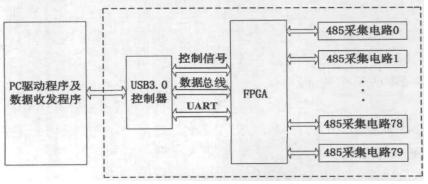

- 多串口数据通信技术主要研究数据的多串口采集、存储和处理。由于串口通信技术的广泛应用,使得多串口采集卡一直是研究的热点,从早期的基于PCI总线的多串口数据采集卡到后来的基于USB的多串口数据采集卡,以及现在的基于USB3.0的多串口数据采集卡。

PCI采集卡由于使用不方便,逐渐被淘汰,目前USB传输系统被广泛应用。USB2.0理论传输速度为480Mb/s,而USB3.0的传输速率可高达5Gb/s,且在USB2.0的基础上又增加了超高速传输模式。本文设计的系统中有80个485传输通道,每个通道的速率

- 关键字:

USB3.0 FPGA PCI

- 广东高云半导体科技股份有限公司(以下简称“高云半导体”)今日宣布推出拥有完全自主知识产权的现场可编程门阵列(FPGA)朝云™产品系列。可广泛用于通信网络、工业控制、工业视频、服务器、消费电子等领域,帮助用户降低开发风险,迅速克服产品上市时间带来的挑战。

朝云™产品系列在目前FPGA市场上处于中密度范围,逻辑单元从18K LUT到100K LUT。其中有两个家族产品,分别为GW2A和GW3S。前者采用台积电(TSMC)的55nm工艺,后者采用台积电的

- 关键字:

高云 FPGA GW2A

- 2014年10月29日 上海IC-China讯,广东高云半导体科技股份有限公司(简称高云半导体)今日召开新产品发布会,宣布推出拥有我国完全自主知识产权的三大产品计划:

现场可编程门阵列(FPGA)朝云™产品系列;

现场可编程门阵列(FPGA)云源™设计软件;

基于现场可编程门阵列(FPGA)的IP软核平台—星核计划。

拥有完全自主知识产权的现场可编程门阵列(FPGA)朝云™产品系列。

- 关键字:

FPGA 高云 朝云

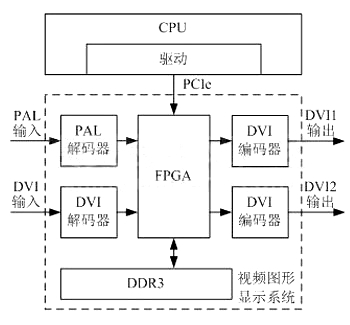

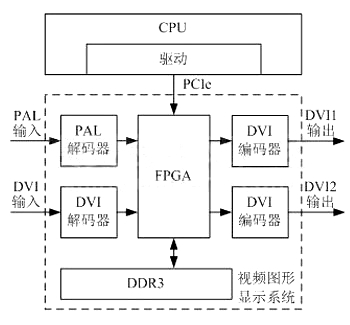

- 随着航空电子技术的不断发展,现代机载视频图形显示系统对于实时性等性能的要求日益提高。常见的系统架构主要分为三种:

(1)基于GSP+VRAM+ASIC的架构,优点是图形ASIC能够有效提高图形显示质量和速度,缺点是国内复杂ASIC设计成本极高以及工艺还不成熟。

(2)基于DSP+FPGA的架构,优点是,充分发挥DSP对算法分析处理和FPGA对数据流并行执行的独特优势,提高图形处理的性能;缺点是,上层CPU端将OpenGL绘图函数封装后发给DSP,DSP拆分后再调用FPGA,系统的集成度不高

- 关键字:

FPGA DSP ASIC

fpga)介绍

您好,目前还没有人创建词条fpga)!

欢迎您创建该词条,阐述对fpga)的理解,并与今后在此搜索fpga)的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473