- 东亚地区长程演进计画(LTE)设备需求,驱动现场可编程闸阵列(FPGA)业者营收攀升。2014年中国大陆及台湾陆续启动LTE商转,带动庞大的LTE设备购置及基础建设投资潮,深耕通讯领域有成的FPGA业者也趁着这波潮流搭上顺风车,大发LTE财。

赛灵思(Xilinx)亚太区销售与市场副总裁杨飞表示,中国大陆于2013年底发放LTE营运牌照后,业界都在引颈期盼这个全球最大的内需市场将为LTE供应链带来一波新气象;果不其然,2014年中国大陆三大电信营运商陆续启动LTE商转,加上台湾LTE网路也随后开

- 关键字:

Xilinx FPGA LTE

- 因应网路速度的提升与资料呈现暴炸性的成长,资料中心无疑是IT领域下一波决战的主战场,这从网路服务业者,如Google、脸书与亚马逊近期的动作来看,就能窥见端倪。

Xilinx亚太区销售及市场副总裁杨飞

就晶片供应商而言,过去一直以来,大多都是CPU与GPU业者扮演主导角色,如今FPGA(可编程逻辑闸阵列)业者们,也对该应用领域有相当积极的动作。Xilinx亚太区销售及市场副总裁杨飞便表示,伺服器业者们都在思考如何降低功耗的问题,再加上伺服器或是资料中心本身也都会

- 关键字:

Altera FPGA GPU

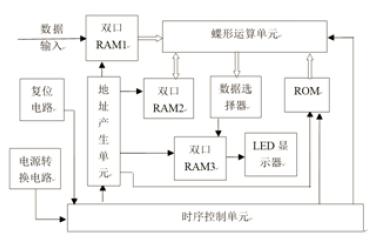

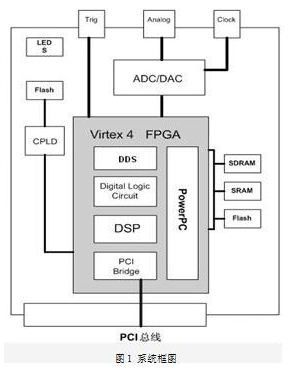

- 针对传统管道漏磁检测器检测精度的不足,提出了新式的基于FPGA的高精度管道漏磁检测系统设计,以适应813mm管径的管道检测任务。主要介绍了系统逻辑设计,实现了多达400路传感器漏磁检测信号的采集与存储。该设计融合了多种总线协议,可有效解决管道漏磁检测中的采集速率、功耗和精度的问题。经实验验证,方案切实可行,为设计高精度管道漏磁检测系统提供了新的解决方案。

基于FPGA的多传感器管道内漏磁检测系统.pdf

- 关键字:

FPGA 传感器

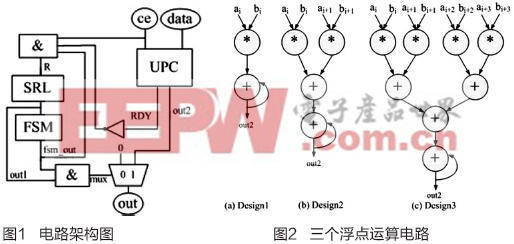

- 摘要:随着集成电路产业的迅速发展,集成电路设计的安全性越来越受重视,电路设计盗用等知识产权(IP)侵权行为严重损害了设计者和消费者的权益,阻碍了集成电路产业的发展。本文提出了一种有效保护IP核的方法,通过设计一个保护电路,控制功能电路运行结果的输出,在消费者未取得合法授权时,功能电路无法正常工作,从而达到了保护电路的目的。本文将该保护方法运用在实际的电路上,进行仿真并验证了该方法的有效性。

引言

随着片上系统SoC的迅速发展,IP复用的知识产权保护问题日益严重,危害了设计者和消费者的权益[

- 关键字:

IP核 FPGA 寄存器 IP固核 RDY 201412

- 摘要:制造业革命需要大量的工业机器人、PLC、电机,FPGA及模拟芯片厂商需要因应新的工业需求,推出新型的芯片或模块解决方案。

机器人需要新型芯片及模组

世界机器人市场

现代工业正逐渐由“工业自动化”向“工业智能化”迈进,传统制造业正开启“智”造之门。实现工业智能化需要更高安全性、可靠性的工业以太网、更高精确度的运动控制技术以及马达控制解决方案等,机器人就是综合体现这种智能化的设备之一。

据统计,世界机器人

- 关键字:

机器人 以太网 FPGA PLC 201412

- 随着集成电路的飞速发展,在图像处理,通信和多媒体等很多领域中,数字信号处理技术已经被广泛应用。快速傅立叶变换(FFT)算法的提出,使得数字信号处理的运算时间上面缩短了好几个数量级。因此对FFT算法及其实现方法的研究具有很强的理论和现实意义。

1 FFT算法及其实现方法

现场可编程门阵列FPGA是一种可编程使用的信号处理器件,其运算速度高,内置高速乘法器可实现复杂累加乘法运算;同时其存储量大,无需外接存储器就可实现大量数据运算;而且算法实现简单,通过VHDL编程语言可轻松实现功能开发,缩短了

- 关键字:

FPGA FFT

- 开创性FPGA软件供应商Plunify® Pte. Ltd.今日宣布,从早期风险资本投资公司Lanza techVentures获得一轮融资。

此次所获投资将被用于发展Plunify的销售和技术支持渠道,扩展其市场团队,以推动专用于FPGA设计的InTimeTM时序收敛加速软件。Lanza techVentures总经理Lucio Lanza将成为Plunify董事会的一员。Lanza techVentures的自由合伙人Mark Templeton将担任公司顾问。

Lanza t

- 关键字:

FPGA Plunify 时序收敛

- 现代数字系统中,异步FIFO是一种被广泛应用于跨时钟域进行数据传输的有效方式。异步FIFO主要应用于两种不同时钟域的数据传输,这意味着数据的写入在一个时钟域,而数据的读出却在另一个时钟域,两个时钟完全异步[1]。现代通信系统中,特别是在移动通信系统中,人们对于节能型的产品提出了更高的要求。随着技术的发展,FPGA的技术、性能、稳定性等指标已经得到很大提高,同时FPGA厂商为不同的应用开发提供了各种IP核,大大减少了产品的开发周期,在各大FPGA厂商中,Xilinx的IP核应用比较广泛。但其IP核却没有

- 关键字:

FIFO FPGA

- 致力于在电源、安全、可靠和性能方面提供差异化半导体技术方案的领先供应商美高森美公司(Microsemi Corporation)祝贺欧洲太空总署(ESA)、美国国家航空航天局(NASA)和其合作伙伴的罗塞塔号(Rosetta)探测器成功实现了观测67P/Churyumov-Gerasimenko彗星的任务目标。

超过15,000个美高森美高可靠性创新太空产品,比如跨越多项技术的FPGA、二极管、晶体管和集成电路用于这个长达10年、跨越40亿英里的关键任务应用中,并且继续支持该任务进行多种研究项目

- 关键字:

美高森美 FPGA 晶体管

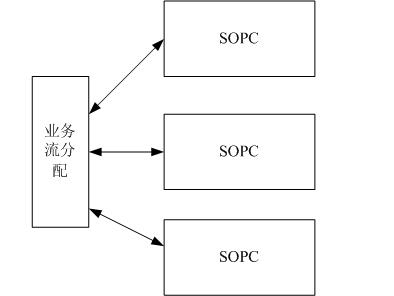

- 通常认为,SOPC是FPGA设计中的鸡肋,“弃之可惜,食之无味”。诚然,SOPC一直不是FPGA的主流应用设计,制约主要因素则是性能,因为作为处理器使用时,处理器主频是其应用范围的瓶颈(SOPC的软核处理器一般运行几十兆到百兆,而一般的嵌入式处理器系统在几百兆到Ghz的主频)。但是若因此说成“鸡肋”,也确实夸张。厂家推出SOPC的设计,其优点主要有一下几点,其一:是差异化竞争的需要。其二,扩大应用范围,争取更多的软件工程师能够从事FPGA设计。其三,可以

- 关键字:

FPGA SOPC

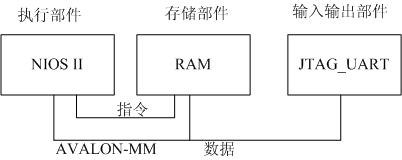

- 从最初的占地170平方的第一代ENIAC计算机开始,计算机开始了不断集成化、小型化的发展之旅。现今在单一芯片内部已经能够集处理器,存储,各型协处理器等,从而形成的强大的单芯片的片上系统(SOC),而这些片上系统已存在于生活的方方面面。因此FPGA内部支持片上系统,也算不上是新奇的事情了。ALTERA和XILINX已各自推出了各自应用片上系统(FPGA领域称之为SOPC,因此其片上系统可以根据业务需求来定义)。

只需几K的资源,就能实现一个SOC的最小系统,对于FPGA工程师来说,没什么比这个更有

- 关键字:

FPGA SOC NIOSII

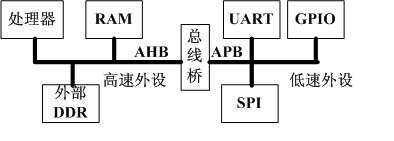

- 如果说在PC时代,垄断PC江湖的是WINTEL(微软和英特尔),那么在移动互联网时代,最具有这个潜质的就是谷歌的andriod操作系统和ARM芯片。基于ARM公司授权的各型ARM处理器,基本上在各型嵌入式终端设备占据了垄断地位。“背靠大树好乘凉”,因此,用于作为ARM处理做片上系统互联的AMBA总线标准亦成为业界应用最广泛的标准。

AMBA总线事实上为三个总线标准的合集,分别是AHB、ASB、APB。ASB已逐渐被AHB所取代,现在使用最广泛的为AHB和APB总线,以及最

- 关键字:

FPGA ARM xilinx

- 开创性FPGA软件供应商Plunify® Pte. Ltd.今日发布其支持Altera 的FPGA和SoC的InTimeTM设计优化软件。

Plunify的InTime软件借助于运算资源和机器学习技术,快速地生成解决设计问题的优化策略。

Altera软件和IP市场总监Alex Grbic说,“我们很高兴Plunify能成为我们的合作伙伴。与Plunify这样的公司合作使我们可以向客户提供更多相互支持的解决方案。”

Plunify的InTime软件能为A

- 关键字:

FPGA Altera SoC

- 软件无线电的出现,是无线电通信从模拟到数字、从固定到移动后,由硬件到软件的第三次变革。简单地说,软件无线电就是一种基于通用硬件平台,并通 过软件可提供多种服务的、适应多种标准的、多频带多模式的、可重构可编程的无线电系统。软件无线电的关键思想是,将AD(DA)尽可能靠近天线和用软件来 完成尽可能多的无线电功能。

蜂窝移动通信系统已经发展到第三代,3G系统进入商业运行一方面需要解决不同标准的系统间的兼容性;另一方 面要求系统具有高度的灵活性和扩展升级能力,软件无线电技术无疑是最好的解决方案。用ASI

- 关键字:

FPGA ASIC

fpga)介绍

您好,目前还没有人创建词条fpga)!

欢迎您创建该词条,阐述对fpga)的理解,并与今后在此搜索fpga)的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473