- 信号发生器又称为波形发生器是一种常用的信号源并且广泛应用于电子电路、通信、控制和教学实验等领域的重要仪器之一。为了降低传统函数信号发生器成本,改善信号发生器低频稳定性。笔者结合FPGA和51单片机产生0.596 Hz频率精度函数信号。笔者设计通过51单片机控制函数信号类型以及相关参数,用户可通过按键设置需要的波形、波形幅度、波形频率以及方波的占空比、相位。本文设计方案不仅具有良好的经济前景,也可以为当代高等教育深化改革做一个参考方向。

1 系统设计方案

1.1 系统硬件设计

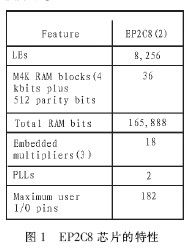

本文中设

- 关键字:

FPGA 51单片机

- 7.3 ModelSim的仿真流程

7.3.1 ModelSim的安装

ModelSim的最新版本可以从互连网上免费得到,需要购买的只是License文件。ModelSim的下载地址为http://www.model.com/。打开网站页面后可以点击Download,用户填写完一张表格以后可以得到一个小时的下载时间。

获得License的方法有很多种。

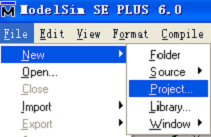

首先可以在线申请License文件,选取“开始→程序→ModelSim SE 5.8c&rar

- 关键字:

FPGA ModelSim

- 7.2 ModelSim仿真工具简介

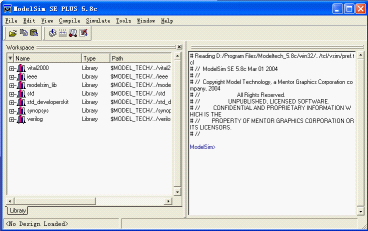

ModelSim是Model Technology(Mentor Graphics的子公司)的DHL硬件描述语言的仿真软件,该软件可以用来实现对设计的VHDL、Verilog或者是两种语言混合的程序进行仿真,同时也支持IEEE常见的各种硬件描述语言标准。

无论从友好的使用界面和调试环境来看,还是从仿真速度和仿真效果来看,ModelSim都可以算得上是业界最优秀的HDL语言仿真软件。它是惟一的单内核支持VHDL和Verilog混合仿真的仿真器,是做FPG

- 关键字:

FPGA ModelSim

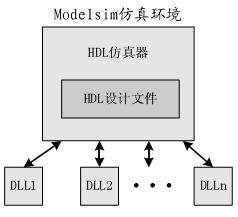

- 1、Modelsim 及 FLI接口介绍

Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述语言仿真软件,可以实现 VHDL, Verilog,以及 VHDL-Verilog 混合设计的仿真。除此之外,Modelsim还能够与 C 语言一起实现对 HDL 设计文件的协同仿真。同时,相对于大多数的 HDL 仿真软件来说,Modelsim 在仿真速度上也有明显优势。这些特点使 Modelsim 越来越受到 EDA设计者、尤其是 FPGA

- 关键字:

Modelsim FPGA

- 信号发生器是一种能提供各种频率、波形和输出电平电信号的设备。在测量各种电信系统或电信设备的振幅特性、频率特性、传输特性及其它电参数时,以及测量元器件的特性与参数时,用作测试的信号源或激励源。

无线电导航数字信号源的系统设计,完整参考方案

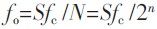

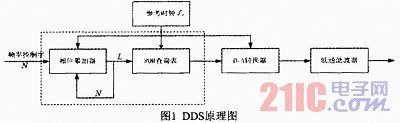

本无线电导航数字信号源总体设计思想采用直接数字频率合成器(DDS)技术,设计精确的时钟参考源精度、频率和相位累加器字长和正弦波函数表,实现研制技术要求的输出频率变化范围、频率变化步长和频率精度的调制正弦信号形式。

基于DDFS的程控音频仪器测试信号源

- 关键字:

无线电 FPGA

- 引言

近年来电子信息技术飞速发展,使得各领域对信号源的要求不断提高,不但要求其频率稳定度和准确度高,频率改变方便,而且还要求可以产生任意波形,输出不同幅度的信号等。DDFS技术是自上世纪70年代出现的一种新型的直接频率合成技术。DDFS技术是在信号的采样定理的基础上提出来的,从“相位”的概念出发,进行频率合成,不但可利用晶体振荡的高频率稳定度、高准确度,且频率改变方便,转换速度快,便于产生任意波形等,因此,DDFS技术是目前高精密度信号源的核心技术。

1 DDFS技

- 关键字:

FPGA DDFS

- 0 引言

跳频通信具有较强的抗干扰、抗多径衰落、抗截获等能力,已广泛应用于军事、交通、商业等各个领域。频率合成器是跳频系统的心脏,直接影响到跳频信号的稳定性和产生频率的准确度。目前频率合成主要有三种方法:直接模拟合成法、锁相环合成法和直接数字合成法(DDS)。直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参考频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗高,目前已基本不用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算

- 关键字:

DDS FPGA

-

测试平台设计

本实验主要对数码管驱动引脚的状态与预期进行比较和分析,通过仿真,验证设计的正确性和合理性。数码管驱动模块的testbench如下所示:

`timescale 1ns/1ns

module DIG_LED_DRIVE_tb;

reg [23:0]data;

reg clk;

reg rst_n;

wire [7:0]seg;

wire [2:0]sel;

DIG_LED_DRIVE DIG_LED_DRIVE

- 关键字:

FPGA 动态扫描

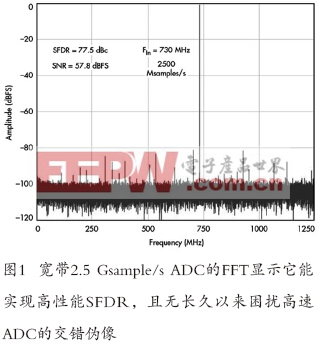

- 随着模数转换器(ADC)的设计与架构继续采用尺寸更小的过程节点,一种新的千兆赫ADC产品应运而生。能以千兆赫速率或更高速率进行直接RF采样且不产生交织伪像的ADC为通信系统、仪器仪表和雷达应用的直接RF数字化带来了全新的系统解决方案。

最先进的宽带ADC技术可以实现直接RF采样。就在不久前,唯一可运行在GSPS (Gsample/s)下的单芯片ADC架构是分辨率为6位或8位的Flash转换器。这些器件能耗极高,且通常无法提供超过7位的有效位数(ENOB),这是由于Flash架构的几何尺寸与功耗限

- 关键字:

ADC RF 转换器 LVDS FPGA

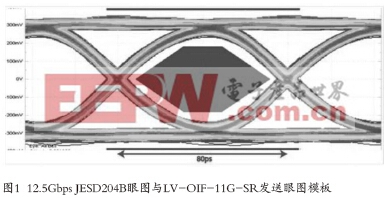

- 1 为不同应用提供不同选择

对于数据转换器的高速串行传输,不同的应用有不同的选择。十多年来,数据转换器制造商一直选择LVDS作为主要差分信号技术。尽管有些LVDS应用可使用更高的数据速率,但目前该市场上的转换器厂商可提供的最大LVDS数据速率仍然为0.8至1 Gbps。LVDS技术一直难以满足转换器的带宽要求。LVDS受TIA/EIA 644A规范控制,这是一项LVDS核心制造商的行业标准。该规范可作为设计人员的最佳实践指南,提高不同厂商的LVDS发送器及接收器兼容性。同样,没有完全遵守LVDS

- 关键字:

JESD204B LVDS 转换器 FPGA PHY

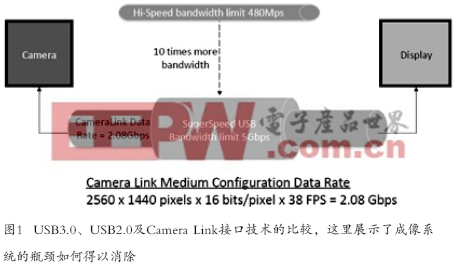

- 高清图像质量已经快速成为现代家庭中多媒体产品的标准配置。在该领域之外的许多应用中,更高的分辨率、更好的对比度、更大的色深和更快的帧率也都越来越受欢迎,这些应用包括安保、医疗成像和工厂生产线检测系统等等。当然,尽管增强型成像技术在不久的将来更加流行似乎是板上钉钉的事情,但这将取决于支持更高数据传输能力的先进半导体技术的发展。本文将以实例阐述半导体技术所取得的进展。

虽然USB连接标准开始并没有引起太多关注,但从上世纪90年代中期第一次脱颖而出已经改变了很多,它现在已经远远不只是为低数据速率的鼠标和

- 关键字:

USB FIFO 缓冲器 FPGA 显示器

- 领先的技术分销商骏龙科技有限公司发布了基于Altera MAX® 10的“Mpression Odyssey(奥德赛)”物联网开发套件和电机驱动方案。Altera的MAX® 10 FPGA在低成本、单芯片、瞬时上电的可编程逻辑器件中提供了先进的处理能力,骏龙科技推出的产品进一步验证了MAX® 10 FPGA的卓越性能,并进一步丰富了Altera公司的工业解决方案。

“Mpression Odyssey(奥德赛)”开发套件是一

- 关键字:

骏龙科技 物联网 FPGA

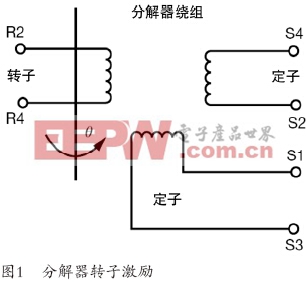

- 1 编码器和分解器的类型

编码器分为增量和绝对两个基本类别。增量编码器可以监控轮轴上的两个位置,可以在轮轴每次经过这两个位置时产生A或B脉冲。独立的外部电动计数器然后从这些脉冲解读出转速和旋转方向。虽然适用于众多应用,但是增量式计数器确实存在某些不足。例如,在轮轴停转情况下,增量编码器在开始运行之前必须首先通过调回到某个指定校准点来实现自身校准。另外,增量式计数器易受到电气干扰的影响,导致发送到系统的脉冲不准确,进而造成旋转计数错误。不仅如此,许多增量编码器属于光电器件,如果对目标应用有影响,则

- 关键字:

编码器 分解器 RDC FPGA 脉冲

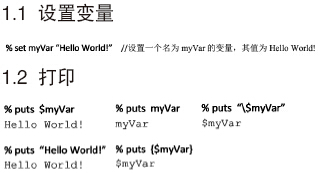

- Xilinx的新一代设计套件 Vivado 相比上一代产品 ISE, 在运行速度、算法优化和功能整合等很多方面都有了显著地改进。 但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为了快速掌握 Vivado 使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到 Vivado 的信心。

本文介绍了 Tcl 在 Vivado 中的基础应用,希望起到抛砖引玉的作用,指引使用者在短时间内快速掌握相关技巧,更好地发挥 Vivado 在 FPGA 设计中的优势。

1

- 关键字:

Xilinx VivadoTcl FPGA cells

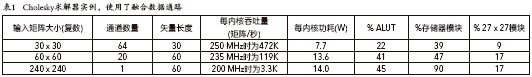

- 1 FPGA浮点运算推陈出新

以往FPGA在进行浮点运算时,为符合IEEE 754标准,每次运算都需要去归一化和归一化步骤,导致了极大的性能瓶颈。因为这些归一化和去归一化步骤一般通过FPGA中的大规模桶形移位寄存器实现,需要大量的逻辑和布线资源。通常一个单精度浮点加法器需要500个查找表(LUT),单精度浮点要占用30%的LUT,指数和自然对数等更复杂的数学函数需要大约1000个LUT。因此随着DSP算法越来越复杂,FPGA性能会明显劣化,对占用80%~90%逻辑资源的FPGA会造成严重的布线拥

- 关键字:

Altera FPGA LUT DSP 数据通路

fpga)介绍

您好,目前还没有人创建词条fpga)!

欢迎您创建该词条,阐述对fpga)的理解,并与今后在此搜索fpga)的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473