为实现目标识别与跟踪的应用目的,在基于TMS320DM642的FIFO基础上扩展存储空间,提出一种基于FPGA实现SDRAM控制器的方法。分析所用SDRAM的特点和工作原理,介绍FPGA中SDRAM控制器的组成和工作流程,给出应用中读SDRAM的时序图。FPGA采用模块化设计,增强SDRAM控制器的通用性,更方便地满足实际需求。

关键字:

FPGA FIFO

随着数字电子系统设计规模的扩大,一些实际应用系统中往往含有多个时钟,数据不可避免地要在不同的时钟域之间传递。如何在异步时钟之间传输数据,是数据传输中一个至关重要的问题,而采用FIFO正是解决这一问题的

关键字:

FPGA FIFO

本文采用CPLD实现了AD芯片、高速FIFO存储器以及MCU之间的接口电路。实验表明,该电路工作稳定可靠,且通用性强,易于移植到其它数据采集系统中。同时,QuartusII等嵌入式技术的使用,简化了开发流程,提高了设计效率。目前,该电路已成功应用于某数据采集系统中。

关键字:

8323 FIFO CPLD ADS

摘 要:首先介绍了多路数据采集系统的总体设计、FIFO芯片IDT7202。然后分别分析了FIFO与CPLD、AD接口的设计方法。由16位模数转换芯片AD976完成模拟量至位数字量的转换,由ATERA公司的可编程逻辑器件EPM7256A完成对数

关键字:

FIFo 多路数据采集 系统

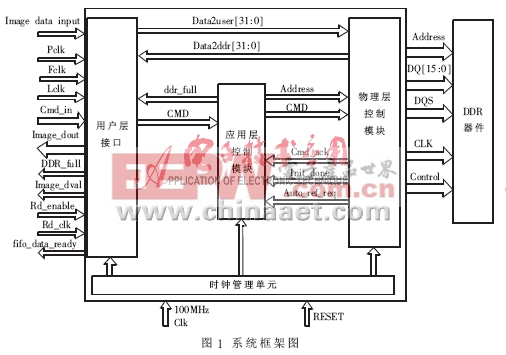

随着半导体传感器技术的发展,在实际应用中越来越多地用到了高帧频、大面阵的CCD相机以获取高质量、高分辨率的图像数据。以分辨率为1K×1K、帧频为200f/s、8bit灰度级的相机为例,其图像数据流速率就将高达200MB/s,

关键字:

实现 图像 高速 DDR 基于 DDR存储控制器 高速缓存 FIFO

PCI总线是Intel公司推出的一种高性能局部总线,其数据总线为32位,且可扩展为64位,最大数据传输速率为132~264MB/s,是目前使用非常普遍的一种总线。因PCI 协议比较复杂,较难掌握,故PCI总线扩展卡的开发较ISA总线等其它

关键字:

9054 FIFO PCI 性能分析

软件无线电数字中频接收机通常采用可编程数字下变频器DDC和DSP的实现方案。中频模拟信号通过A/D数字化,送入DDC混频、抽取滤波处理,DSP接收到的是DDC输出的低速零中频信号,其后的解调、译码、信号识别等算法都可以

关键字:

数据传输 实现 高速 DSP FIFO DDC 基于 FIFO DDC DSP

基于DSP的高速数据采集与处理系统,在电子测量中,常常需要对高速信号进行采集与处理。例如,在光传感技术中,对光脉冲散射信号的测量;在雷达工程中,对电磁脉冲信号的测量等,就需要对高速信号进行采集与处理,而且对此类高速信号的测量,往往对数据采集与处

关键字:

处理 理系 数据采集 高速 DSP 基于 DSP 高速A/D FIFO 异步串行通讯

笔者在参加国家“863”重大专题项目“高速密码芯片及验证平台系统”的过程中,遇到了将IPV6数据包的包头...

关键字:

FPGA IPV6 FIFO

1 引言

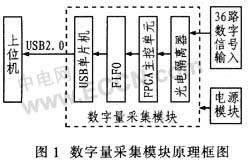

测控系统常常需要处理所采集到的各种数字量信号。通常测控系统采用通用MCU完成系统任务。但当系统中采集信号量较多时,仅依靠MCU则难以完成系统任务。针对这一问题,提出一种基于FPGA技术的多路数字量采集模块。利用FPGA的I/O端口数多且可编程设置的特点,配以VHDL编写的FPGA内部逻辑,实现采集多路数字量信号。

2 模块设计方案

2.1 功能要求

该数字量采集模块主要功能是采集输入的36路数字及脉冲信号,并将编帧后的信号数据上传给上位机,上位机经解包处理后显示信号相

关键字:

FPGA 数字量采集 测控 USB单片机 MCU FIFO

语音激活检测VAD(Voice Activity Detection)是一种通过特定的判决准则判断语音中出现的停顿和静默间隔,检测出有效语音部分的技术。运用这种技术可以在确保语音质量的前提下,对不同类别的语音段采用不同的比特数进行编码,从而降低语音的编码速率。由于在双工移动通信系统中,一方只有35%的时间处于激活状态[1],如何降低静音期的编码速率对于减少传输带宽、功率以及容量具有积极的作用,因此VAD技术在语音通信领域具有重要的使用价值。随着适合于变比特率语音编码的CDMA和PRMA等多址技术的出现

关键字:

FPGA VAD 短时能量 短时过零率 FIFO 滤波器

随着信息科学的飞速发展,数据采集和存储技术广泛应用于雷达、通信、遥测遥感等领域。在高速数据采集系统中,由ADC转换后的数据需要存储在存储器 中,再进行相应的处理,保证快速准确的数据传输处理是实现高速数据采集的一个关键。由于高速ADC的转换率很高,而大容量RAM相对ADC输出速度较慢, 保持高速数据存储过程的可靠性、实时性是一个比较棘手的问题。对于数据采集系统中的大容量高速度数据存储、传输,本文提出一种基于FPGA的多片RAM实 现高速数据的存储和传输的方案,并应用于1GS/s数据采集系统中,实现了以低

关键字:

数据采集 存储 传输 ADC SRAM RAM FIFO

在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态[1]。在有大量的数据需要进行跨时钟域传输且对数据传输速度要求比较高的场合,异步FIFO是一种简单、快捷的解决方案。

异步FIFO用一种时钟写入数据,而用另外一种时钟读出数据。读写指针的变化动作由不同的时钟产生。因此,对FIFO空或满的判断是跨时钟域的。如何根据异步的指针

关键字:

FIFO 异步 Verilog HDL IC 亚稳态

fifo介绍

采用FIFO方式时,信息被以所收到的次序进行传输。

表示信息存储的一种数据结构,含义是先进入的对象先取出。队列(Queue )就是基于这种性质实现的。

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473