- DSP内嵌PLL中的CMOS压控环形振荡器设计,本文设计了一种应用于DSP内嵌锁相环的低功耗、高线性CM0S压控环形振荡器。电路采用四级延迟单元能方便的获得正交输出时钟,每级采用RS触发结构来产生差分输出信号,在有效降低静态功耗的同时.具有较好的抗噪声能力。在延迟单元的设计时。综合考虑了电压控制的频率范围以及调节线性度,选择了合适的翻转点。 仿真结果表明.电路叮实现2MHz至90MHz的频率调节范围,在中心频率附近具有很高的调节线性度,可完全满足DSP芯片时钟系统的要求。

- 关键字:

振荡器 设计 环形 CMOS 内嵌 PLL DSP

- 摘要:通过对DDS的信号模拟器设计的研究,不仅设计出能够实现普通射频合成信号源的功能,正如能够在幅度、频率等方面对所需生成的信号加以控制,也能够实现定频、扫频以及跳频等输出方式上的选择。同时,该系统增加

- 关键字:

DDS 信号模拟器

- 1引言直接数字频率合成DDS(DirectDigitalSynthesizer)是基于奈奎斯特抽样定理理论和现代器件生...

- 关键字:

FPGA DDS 信号源 设计

- 基于模型的DDS芯片设计与实现,摘要:介绍了一种基于模型的DDS芯片的设计方法。根据DDS基本原理,在MATLAB环境下建立模型,用System Generator产生VHDL程序,并在ISE软件中编写仿真和控制程序,最后在Spartan-3E Starter Kit开发板上实现设计。与传统的

- 关键字:

设计 实现 芯片 DDS 模型 基于

- 基于DSP和DDS的三维感应测井高频信号源实现, 引言 高频信号源设计是三维感应测井的重要组成部分。三维感应测井的原理是利用激励信号源通过三个正交的发射线圈向外发射高频信号,再通过多组三个正交的接收线圈,得到多组磁场分量,从而准确测量地层各向异性

- 关键字:

高频 信号源 实现 测井 感应 DSP DDS 三维 基于

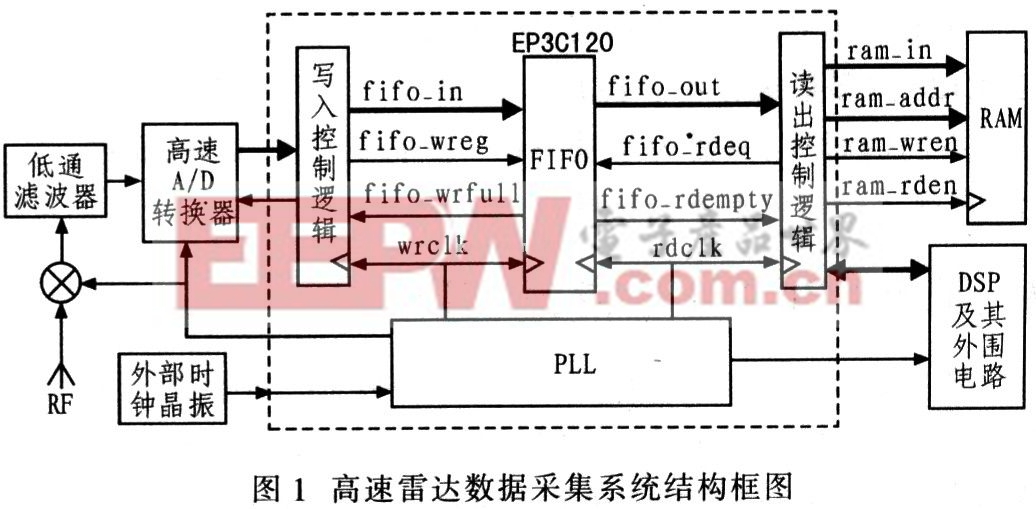

- 异步FIFO和PLL在高速雷达数据采集系统中的应用,将异步FIFO和锁相环应用到高速雷达数据采集系统中用来缓存A/D转换的高速采样数据,解决嵌入式实时数据采集系统中,高速采集数据量大,而处理器处理速度有限的矛盾,提高系统的可靠性。根据FPGA内部资源的特点,将FIFO和锁相环设计在一块芯片上。因为未使用外挂FIFO和PLL器件,使得板卡设计结构简单,并减少硬件板卡的干扰。由于锁相环的使用,使得整个采集系统时钟管理方便。异步FIFO构成的高速缓存具有一定通用性,方便系统进行升级维护。

- 关键字:

数据采集 系统 应用 雷达 高速 FIFO PLL 异步

- 自动反馈调节时钟恢复电路设计,0 引言

信息技术的迅猛发展使得人们对数据传输交换的速度要求越来越高,因此,各种高速接口总线规范应运而生,从USBl.1到USB3.0,从PATA到SATA,从PCI总线到PCI―Express,其接口总线速度也由最初的Kbyte发展

- 关键字:

恢复 电路设计 时钟 调节 反馈 自动 PLL 时钟恢复 自动反馈 CDR 高速串行总线

- 基于FPGA和DDS的信号源设计,1 引言

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率

- 关键字:

设计 信号源 DDS FPGA 基于 FPGA,DDS,Verilog HDL

- 介绍了DDS技术的原理和特性,采用DDS芯片AD9833产生正弦波音阶信号构建音源发生器,给出了主要电路和关键程序。

- 关键字:

9833 DDS AD 芯片

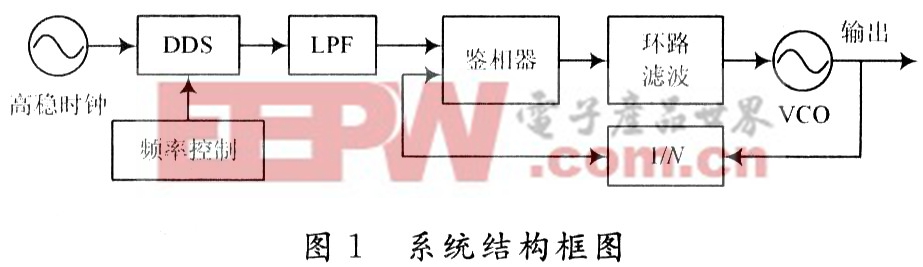

- 由于超宽带信号的带宽很宽,传统的信号产生办法已不能直接应用于超宽带通信。为此,提出一种基于DDS+PLL的Chirp-UWB信号产生方案,该方法联合使用了DDS和PLL两种信号产生技术,优势互补。通过ADS结合Matlab对系统的模型建立和性能分析证明,该方案输出信号性能优良,完全能满足设计要求,并已成功应用于某超宽带通信系统。

- 关键字:

产生 方案 信号 Chirp-UWB DDS PLL 基于 转换器

- 频率合成技术起源于二十世纪30年代,当时所采用的频率合成方法是直接频率合成。它是利用混频、倍频、分频的方法由参考源频率经过加、减、乘、除运算,直接组合出所需要的的频率。它的优点是捷变速度快,相位噪

- 关键字:

DDS 杂散分析 方法

- 介绍基于DDS的信号发生器工作原理和设计过程,并对关键模块及外围电路进行了仿真和误差分析。经功能验证和分析测试,达到了预定的各项技术指标。旨在建立一种以FPGA为核心,功能可裁剪、波形任意调整的高性能信号发生器设计方法。采用该设计法将有效地降低开发成本,提高设计效率,并具有一定的工程指导意义和实用价值。

- 关键字:

FPGA DDS 信号发生器

dds+pll介绍

您好,目前还没有人创建词条dds+pll!

欢迎您创建该词条,阐述对dds+pll的理解,并与今后在此搜索dds+pll的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473