在国内疫情尚还未完全好转的情况下,全球疫情开始逐渐恶化。而日韩疫情的凶猛,更是给全球半导体领域投下了“重磅炸弹”。

关键字:

宏旺半导体 DDR ICMAX

要FPGA与的数字信号采集系统。可以提供大容量的存储空间。提供优秀的系统适应能力。该方案通过计算机并口实现与计算机的通信 ,但是高性能的逻辑分析仪

关键字:

SDRAM FPGA 数字电视信号 采集系统

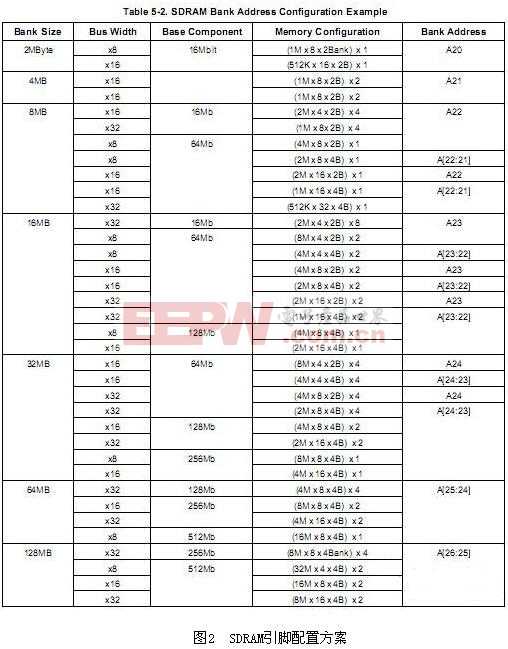

介绍SDRAM电路设计之前先了解下SDRAM的寻址原理。SDRAM内部是一个存储阵列,可以把它想象成一个表格,和表格的检索原理一样,先指定行,再指定列,就可

关键字:

SDRAM 电路设计 寻址原理 存储单元

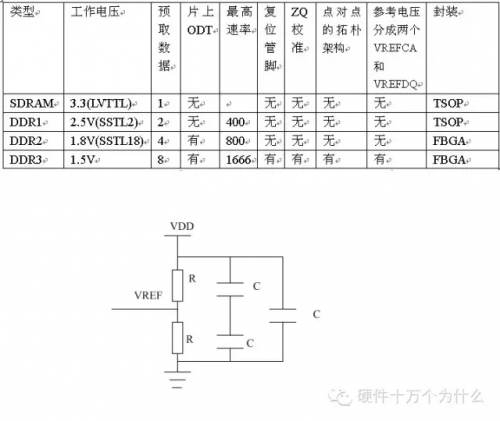

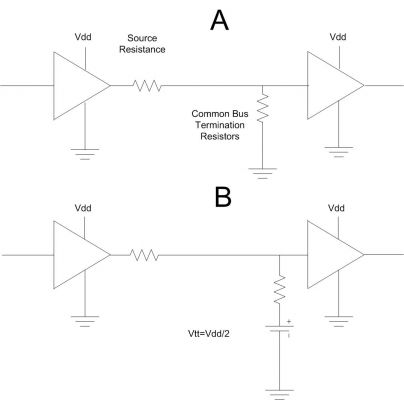

DDR硬件设计要点 1. 电源 DDR的电源可以分为三类: a主电源VDD和VDDQ,主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。 有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。电源电压的要求一般在±5%以内。电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR的电流一般都比较大,所以P

关键字:

DDR,PCB

DDR的种类: 1、DDR SDRAM:Double Data Rate Synchronous Dynamic Random Access Memory,双倍数据率同步动态随机存取存储器; 2、DDR2 SDRAM:Double-Data-Rate Two Synchronous Dynamic Random Access Memory,第二代双倍数据率同步动态随机存取存储器; 3、DDR3 SDRAM:Double-Data-Rate Three Synchronous Dynamic Ra

关键字:

DDR 三星

本文主要介绍的是ARM里的RAM和SDRAM有什么区别,首先介绍了RAM的类别及特点,其次对SDRAM做了详细阐述,最后介绍了RAM和SDRAM的区别是什么。 RAM介绍 Random-Access Memory(随机存取存储器),在计算机的组成结构中,有一个很重要的部分,就是存储器。存储器是用来存储程序和数据的部件,对于计算机来说,有了存储器,才有记忆功能,才能保证正常工作。存储器的种类很多,按其用途可分为主存储器和辅助存储器[或者内存储器和外存储器],主存储器简称内存,内存在电脑中起

关键字:

ARM SDRAM

似乎中国已经要赶上国外主流水准,但是业内却传出DDR内存已经过时,新的内存即将取代,这无疑给国内的DDR内存制造厂商当头一棒。

关键字:

内存 DDR

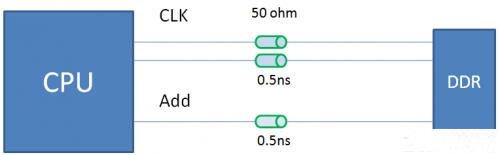

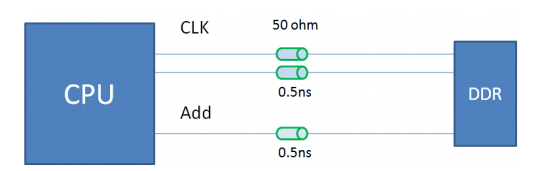

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。那么,时钟信号和地址同时到达接收端,波形的对应关系是什么样的呢?我们通过仿真来看一下具体波形。 建立如下通道,分别模拟DDR3的地址信号与时钟信号。

关键字:

PCB DDR

SDRAM SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。 所谓的影响性能是并不是指SDRAM的带宽,频率与位宽固定后,带宽也就不可更改了。但这是理想的情况,在内存的工作周期内,不可能总处于数据传输的状态,因为要有

关键字:

SDRAM

自从收购SanDisk(闪迪)依赖,西部数据就开始“名正言顺”地进入消费级固态存储市场。与仍保持SanDisk品牌的移动存储产品不同,SanDisk的SSD产品已经改头换面,成为西部数据品牌下的产品。如果说去年所推出的第一代Blue(蓝盘)还有着深厚的SanDisk时代烙印,那么新一代产品则完全诞生于西部数据的体系,SanDisk已经成为其产品的部分零部件供应商。

到目前为止,SSD仍缺乏普及的基础,没有了诸如4K视频这样强烈需求的推动,同时还有利润更高的手机抢资源,一年

关键字:

西部数据 SDRAM

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。那么,时钟信号和地址同时到达接收端,波形的对应关系是什么样的呢?我们通过仿真来看一下具体波形。 建立如下通道,分别模拟DDR3的地址信号与时钟信号。

关键字:

DDR 布线

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。

关键字:

DDR PCB DQS

USB(Universal Serial Bus)是通用串行总线的缩写,因其具有方便易用,动态分配带宽,容错性优越和高性价比等特点,现已成为计算机的主流接口。

关键字:

USB CPU NANDFlash SDRAM

随着高速处理器的不断发展,嵌入式系统应用的领域越来越广泛,高速大容量缓存器被广泛应用于音视频系统中,然而专用的高速大容量缓存芯片价格过于昂贵,传统SDRAM在带宽上已经逐渐无法满足应用.

关键字:

MIMO技术 视频缓存器 DDR

介绍了SDRAM的存储体结构、主要控制时序和基本操作命令,并且结合实际系统,给出了一种用FPGA实现的通用SDRAM控制器的方案。

关键字:

VHDL 状态机 SDRAM

ddr-sdram介绍

您好,目前还没有人创建词条ddr-sdram!

欢迎您创建该词条,阐述对ddr-sdram的理解,并与今后在此搜索ddr-sdram的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473