csp+layout+for+gc0307+fm1 文章

最新资讯

- 直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。 直角走线的对信号的影响就是主要体现在三个方面:一是拐角可以等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射;三是直角尖端产生的EMI。传输线的直角带来的寄生电容可以由下面这个经验公式来计算:C=61W(Er)1/2/Z0在上式中

- 关键字:

PCB Layout

- 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,

- 关键字:

layout PCB设计 直角走线

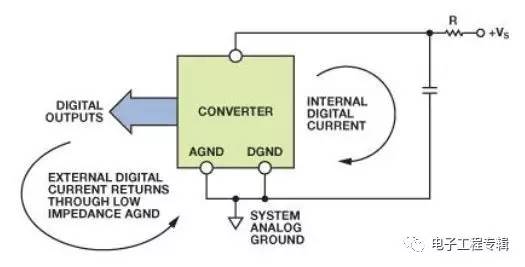

- 接地无疑是系统设计中最为棘手的问题之一。尽管它的概念相对比较简单,实施起来却很复杂,遗憾的是,它没有一个简明扼要可以用详细步骤描述的方法来保证取得良好效果,但如果在某些细节上处理不当,可能会导致令人头痛的问题。 对于线性系统而言,"地"是信号的基准点。遗憾的是,在单极性电源系统中,它还成为电源电流的回路。接地策略应用不当,可能严重损害高精度线性系统的性能。 对于所有模拟设计而言,接地都是一个不容忽视的问题,而在基于PCB的电路中,适当实施接地也具有同等重要的意义。幸运的是,某些

- 关键字:

Layout ADC

- 布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布

- 关键字:

PCB设计 Layout 直角走线 差分走线

- 每个人都想有轻薄的移动设备,这也是新发布的iPhone 6比前几代产品更薄的原因。更薄的设备要求人们开发出更先进的封装技术。遗憾的是,传统的环氧塑料封装不足以构建这些特别薄的设备,因为其封装占位面积比其内部

- 关键字:

芯片级封装 CSP 测试

- 能够应用和生产,继而成为一个正式的有效的产品才是PCB layout最终目的,layout的工作才算告一个段落。那么在layout的时候,应该注意哪些常规的要点,才能使自己画的文件有效符合一般PCB加工厂规则,不至于给企业造成

- 关键字:

PCB Layout 外层线路 内层线路 散热PAD

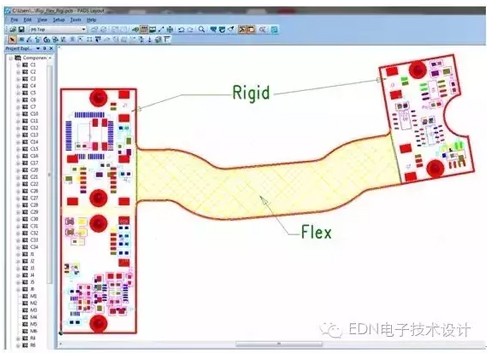

- 我们预想中的完整 PCB 通常都是规整的矩形形状。虽然大多数设计确实是矩形的,但是很多设计都需要不规则形状的电路板,而这类形状往往不太容易设计。本文介绍了如何设计不规则形状的 PCB。

如今,PCB 的尺寸在不断缩小,而电路板中的功能也越来越多,再加上时钟速度的提高,设计也就变得愈加复杂了。那么,让我们来看看该如何处理形状更为复杂的电路板。

如图 1 所示,简单 PCI 电路板外形可以很容易地在大多数 EDA Layout 工具中进行创建。

图 1:常见

- 关键字:

PCB Layout

- CSP的全称是Chip Scale Package,中文意思是芯片级封装、芯片尺寸封装。传统定义为封装体积与LED晶片相同(简称“晶片级封装”),或是体积不大于LED晶片20%且功能完整的封装元件。因为芯片没有经过传统的固晶和焊线这些封装流程,所以CSP又俗称“无封装芯片”。这种叫法最早由中国台湾命名,并传入中国大陆。由于宣称“无封装”,因此CSP广泛引起业内人士的兴趣,成为时下谈论的争议话题。

CSP革了谁的命?

封

- 关键字:

芯片 CSP

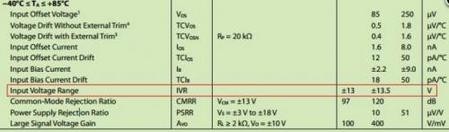

- 运算放大器,对于学工科的学生来说是一个耳熟能详的词。运算放大器作为最通用的模拟器件,广泛运用于信号变换调理、ADC采样前端和电源电路等场合。大家在学习模电课程的时候,都已经学会了运放的设计。然而在使用运放的时候,又有哪些需要注意的呢?今天小编就给大家来讲解一下运放在使用过程中需要注意的六大规则:

1、注意输入电压是否超限

图1-1是ADI的OP07数据表中的输入电气特性的一部分,可以看到在电源电压±15V的条件下,输入电压的范围是±13.5V,如果输入电压超出范

- 关键字:

运算放大器 Layout

- CSP可以被认为是性价比战争催生出来的产物,抛开技术层面来看,其实还是LED产品的优化,那是不是产品结构优化升级后,与原来的产品就一定是取代关系呢?抑或补充。

- 关键字:

OLED CSP

- 倒装有倒装的优势,但正装也有正装的市场,取代一部分可以,全面取代是不现实的,交给市场检验吧。

- 关键字:

COB CSP

- 全球LED照明市场正在稳步增长,预计到2016年的市场规模将从2015年的257亿美元增至305亿美元,LED照明的渗透率将从2015年的31%增至36%。当一边是市场的渗透率不断上升,一边是价格大幅下滑产品沦落论斤卖时,性价比的拼杀显得尤为激烈。 对于“价格为王”,雷利宁认为鸿利光电的确有“王”,但不是价格,而是“技术研发+资源整合”。作为国内最早上市的LED封装企业之一,正是因为拥有了强大的资金实力和研发实力,才为资源整合和降低成本提供了强有力的保证。对于价格战,不应当是牺牲品质称王,而是扩大生

- 关键字:

LED CSP

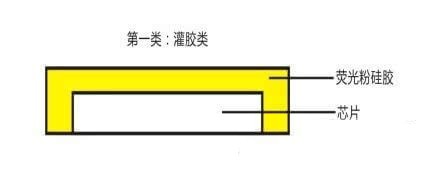

- CSP的全称是ChipScalePackage,中文意思是芯片级封装器件,指的是封装尺寸小于芯片尺寸1.2倍的封装器件,三星出货量最大的LM-131A的芯片尺寸是0.78*0.78mm,封装尺寸是1.42*1.42,严格来说目前主流芯片厂商的封装尺寸都不满足此要求,所以称为CSP有点不严谨。无封装芯片的叫法是从台湾引入,因为芯片没有经过传统的固晶和焊线这些封装流程,因此俗称无封装芯片。

CSP无封装芯片三大主流结构

第一阵营:采用硅胶荧光粉压制而成,五面出光,光效高,但是顶部和四周的色温一

- 关键字:

CSP LED

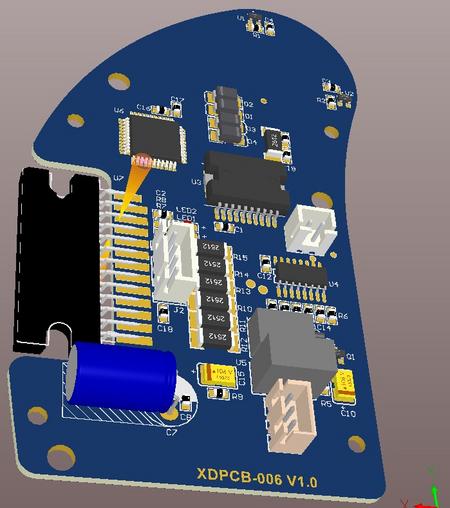

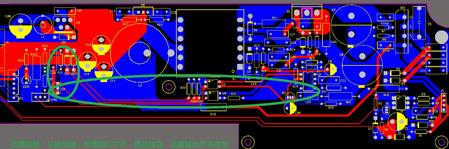

- 关于altium的3d模型,虽说没有什么大用,但也有点小用,先上两副3D PCB图,看起来挺直观的吧。

看起来还是比较直观的,还可以生成.step文件,给我们的结构工程师,这样很容易看出是否与结构干涉。那做这个3D模型难不难呢?其实非常简单。

只要在自己原有的PCB库中,添加一下3D模型就可以了,这样原来PCB板上就会带有3D模型,在2D视图状态下,按一下快捷键“3”就会切换到3D视图状态。

关于如何添加3D封装,百度上

- 关键字:

PCB LAYOUT 3D PCB

- 在模拟电路中,对电磁干扰特别敏感,经常碰到的就是开关电源,它的反馈信号就是模拟信号,很容易受到它自身的开关信号干扰,所以在LAYOUT时要特别注意这一点,否则做出来的电源,轻则纹波太大,重则不能工作。

反馈回路受到的干扰一般分为两种:传导与辐射。针对传导,在元器件布局时就要注意了,不要将反馈回路纠结在开关信号中,反馈信号中的地线,从输出端引出,不要就近原则。让反馈回路独立,远离其他路径。如下图。(此图变压器初级地线有问题)

关于辐射干扰,我认为就是电流变化,在其

- 关键字:

PCB LAYOUT EMI

csp+layout+for+gc0307+fm1介绍

您好,目前还没有人创建词条csp+layout+for+gc0307+fm1!

欢迎您创建该词条,阐述对csp+layout+for+gc0307+fm1的理解,并与今后在此搜索csp+layout+for+gc0307+fm1的朋友们分享。

创建词条

csp+layout+for+gc0307+fm1电路

csp+layout+for+gc0307+fm1相关帖子

csp+layout+for+gc0307+fm1资料下载

csp+layout+for+gc0307+fm1专栏文章

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473