- quartus的IP仿真出错解决方案,大家都知道quartus的IP可以直接拿来用的,大大节省了开发时间,而且其代码是绝对优化的;所有的前奏都操作成功,设置没什么问题,开始对生成的fft.vhd文件进行编译,点击Start Compilation,第一感觉:慢!编译很慢,

- 关键字:

解决方案 出错 仿真 IP quartus

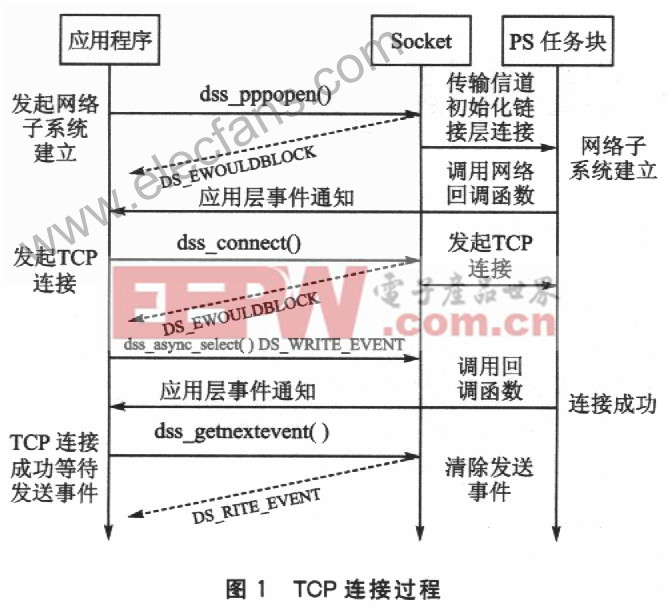

- CDMA是无线通信领域的后起之秀,采用频分编码技术,与基于时分复用的GSM相比具有明显优势。CDMA能够实现从现有通信系统到下一代通信系统的平滑过渡,具有较强的功能伸缩性;可以支持先进的天线技术,通过增加小区覆盖

- 关键字:

IP 协议 TCP 终端 无线 CDMA

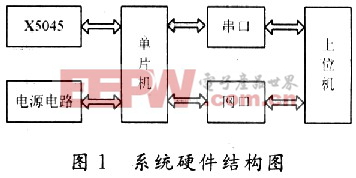

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

I/O口 CPU 97C51

- 还记得当年曾经辉煌的SGI吗?这家标榜自己领导计算机3D世界进步的公司,在沉寂多年后,在今天突然宣布旗下SGI Octane III个人超级电脑。这款超级电脑基于Intel x86处理器,拥有最多80个CPU内核和1TB内存。一举成为当今最为强大的个人计算设备。你要知道的是,Octane II个人超级电脑可是9年前问世的,当时Octane II电脑只有最多2个SGI自家单内核CPU和最大8GB内存。

9年光景,SGI Octane III问世的时候,性能已经和前辈有了天渊之别。 SGI Octa

- 关键字:

超级电脑 CPU

- 国防科大计算机学院“高性能微处理器技术创新团队”,瞄准国家和军队重大战略需求,坚持自主创新,在高性能微处理器技术等方面突破了一系列核心关键技术,填补了国产高性能军用CPU和DSP(数字信号处理器)的空白,让我军武器装备有了“中国芯”。

7月26日,该团队顺利通过了国家教育部组织的创新成果验收。 3年前,该团队入选国家教育部“长江学者和创新团队发展计划”。

3年来,他们在高性能微处理器体系结构、单芯片系统等方面深入探索,

- 关键字:

处理器 CPU

- 在现在的网络通信中,Email服务已经不是现在首选的通信方式了。更多的即时通信,语音服务等,在网络上面层出不穷。那么,现在我们就来说一说IP电话的VoIP技术原理。

基本传输过程

VoIP传统的电话网

- 关键字:

原理 技术 VoIP 电话 IP

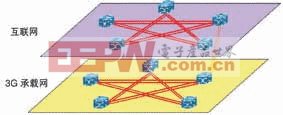

- 毋庸置疑,现代通信网络的发展,是由业务需求和市场需求来决定的,而不是技术的发展。我们回头看看互联网(IP网络)的发展历程,这其中市场推动的痕迹非常明显:这一种六七十年代就已经诞生的IP网络技术,在九十年代

- 关键字:

规划设计 网络 承载 IP 探讨

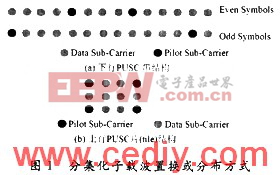

- 基于IEEE 802.16的WiMAX网络的应用正成为业界的讨论热点,IEEE 802.16m更被选为下一代无线通信标准(IMT-advanced)的候选方案之一。在此深入探讨构建基于IP技术的WiMAX应用网络架构。首先分析IEEE 802.16e规范为支持移动性在物理层和媒质接入层引入的增强技术。随后基于移动IP技术和WiMAX网络参考模型给出基于IP的移动WiMAX网络的可行的应用模型。该应用方案可为基于IEEE 802.16技术的应用提供一个参考。

- 关键字:

网络 研究 移动 WiMAX IP 基于 功率模块

- 刚刚与台积电确定长期战略合作关系,ARM今天又宣布已经与微软签订了一份新的ARM架构授权协议。ARM表示,这份协议将有助于拓展两家公司之间的合作关系。自从1997年开始,微软就与ARM在嵌入式、消费级和移动领域的软件、设备方面展开了广泛的合作,促使很多业内企业都在ARM架构产品上提供了更好的用户体验。

由于授权协议存在保密限制,双方都没有透露具体的合作细节,只是说ARM的处理器IP授权模式非常灵活,可在移动设备、家庭电子、工业产品等各种应用领域实现高度集成的方案。

- 关键字:

ARM 处理器 IP

- 嵌入式TCP/IP协议栈在单片机上的实现,给出单片机上网的可行方案,采用SST89E564RD单片机,既提供了网关服务,也实现了在线仿真和下载的功能。由于51单片机资源有限,精简了TCP/IP协议族,在8位单片机上实现了UDP、TCP、ICMP、IP、ARP协议,为嵌入式系统通过以太网接入Internet打下了基础。经过几个月的软硬件测试表明:系统设计合理、稳定可靠。

- 关键字:

机上 实现 单片 协议 TCP IP 嵌入式 收发器

- 一直以来,PC产业处于单一的供应链条中,电脑中包括什么不包括什么,基本上都是英特尔“说 了算”,硬件升级更新的速度也是由英特尔决定的,大部分OEM厂商只能等着上游CPU的更新,来通过控制库存,提高运营效率来争取份额。“游戏规则都是英特尔制定的,全行业为英特尔打工,没有OEM厂商愿意揭开英特尔中国区畸形 的盈利 模式。我在犹豫我要不要成为那个‘揭盖子’的人。”七喜董事副总裁毛骏飙告诉南都记者。毛骏飙还带来了一个让业界吃惊的消息:七喜

- 关键字:

英特尔 CPU

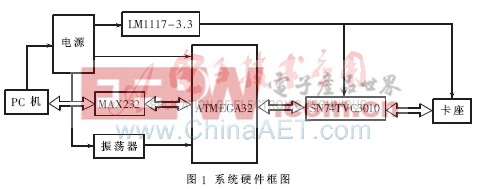

- 针对A类接口的读写器不能对B类CPU卡进行读写的问题,介绍一种可以对3 V的B类卡片进行读写的5 V 接触式IC卡读写器,阐述了其硬件电路结构和单片机固件程序,介绍了对其进行操作的简单上位机软件。实验结果表明,该读写器结构简单、性能稳定,对研制可同时操作3 V/5 V卡片的AB类接口设备有指导意义。

- 关键字:

设计 读写器 接触式 CPU 支持

- 在32位CPU中Load Aligner模块数据通道的设计与实现, 在CPU中,访问寄存器比访问主存速度要快。所以为了减少访问存储器而花的时间或延迟,MIPS4KC处理器采用了Load/Store设计。在CPU芯片上有许多寄存器,所有的操作都由存储在寄存器里的操作数来完成,而主存只有通过L

- 关键字:

通道 设计 实现 数据 模块 CPU Load Aligner 32位

- 在一些恶劣环境和军事应用环境条件下,所应用的计算机比普通商用计算机具有更高、更严的要求,提出基于CPCI总线的CPU主控模块设计方案。该方案严格遵守CPCI规范,利用高性能、低功耗、集成度高的ETX PM模块实现通用计算机的主板功能,采用TI公司的PCI2050B桥电路作为CPCI的接口模块,实现了多级总线扩展结构。该设计方案简化了设计,节省了30%的研制费用,缩短了1/2的研制周期。该模块已经通过舰栽的应用测试,在-40~85℃的环境下,系统工作稳定,各接口应用正常,达到了该项目的技术指标要求。

- 关键字:

CPCI CPU 总线 模块

cpu ip介绍

您好,目前还没有人创建词条cpu ip!

欢迎您创建该词条,阐述对cpu ip的理解,并与今后在此搜索cpu ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473